ZHCSAD2A-OCTOBER 2012-REVISED NOVEMBER 2012

支持睡眠模式的 28V, 0.5A 降压转换器

查询样品: TPS62175, TPS62177

## 特性

- 分布式控制系统 (DCS) 控制的降压转换器™ 拓扑 技术

- 输入电压范围 4.75V 至 28V

- 静态电流典型值4.8µA(睡眠模式)

- 100% 占空比模式

- 有源输出放电

- 电源正常输出

- 500mA 输出电流

- 输出电压范围为 1V 至 6V

- 典型值为 1MHz 的开关频率

- 无缝省电模式转换

- 欠压闭锁

- 短路保护

- 过热保护

- 采用 2mm x 3mm 10 引脚晶圆级小外形尺寸无引 线 (WSON) 封装

## 应用范围

- 普通 12V/24V 负载点电源

- 超移动个人电脑 (PC),嵌入式 PC

- 用于微控制器的低功率电源

- 高效低压降稳压器 (LDO) 架构

- 工业传感器

## 说明

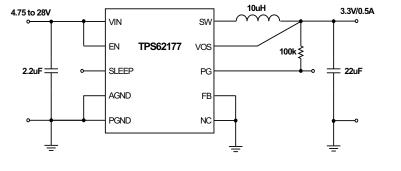

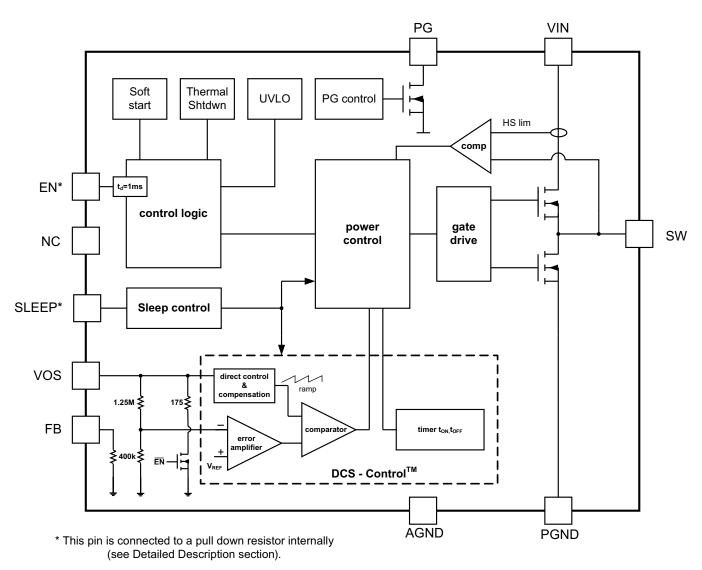

**TPS62175/7** 是一款高效同步降压 **DC-DC** 转换器,此 转换器基于 分布式控制系统 (**DCS**) - 控制的降压转换 器™ 拓扑技术。

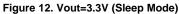

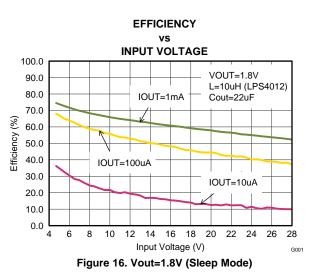

借助于 4.75V 至 28V 的宽工作输入电压,此器件非常适合于由多节锂离子电池以及 12V 和更高阻抗电源轨供电的系统,从而提供高达 500mA 的输出电流。

**TPS62175/7** 在轻负载时自动进入节能模式,以在整个 负载范围内保持高效率。此外,它特有一个为具有高 级节能模式的应用(像超低功耗微控制器)供电的睡眠 模式。电源正常输出可被用于电源排序和/或者加电复 位。

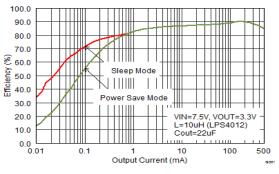

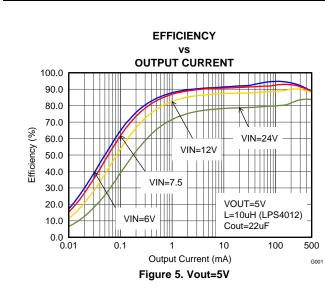

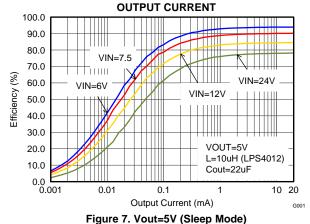

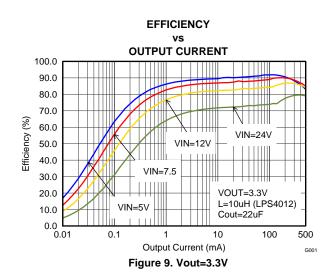

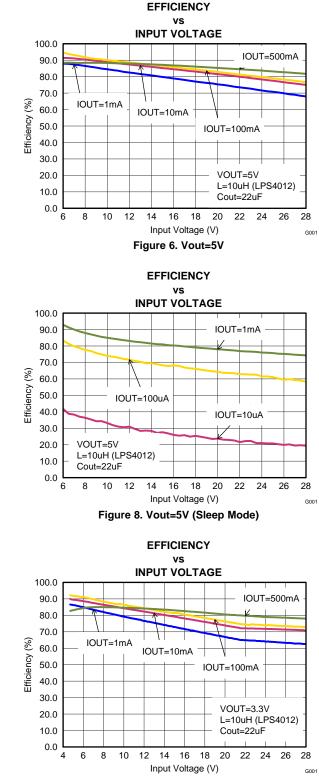

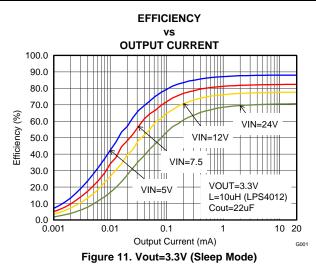

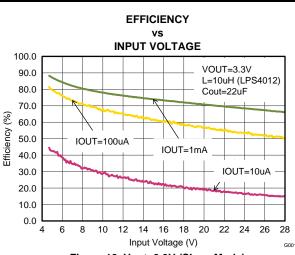

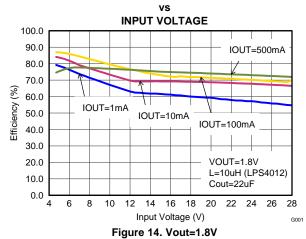

此器件在正常模式特有一个典型值为 22uA 的静态电流,在睡眠模式中此电流值为 4.8uA。 In Sleep Mode, the efficiency at very low load currents can be increased by as much as 20%. 在关断模式中,关断电流少于 2uA 并且输出被有源放电。

提供可调和固定输出电压版本的 TPS62175/7 采用一个小型 2mm x 3mm 10 引脚 WSON 封装。

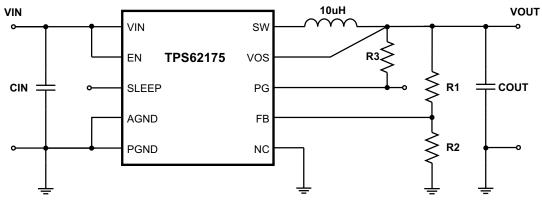

图 1. 典型应用和效率

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. 分布式控制系统 (DCS) - 控制的降压转换器, 分布式控制系统 (DCS) - 控制的降压转换器, or Texas Instruments.

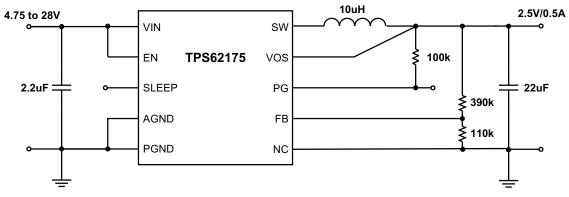

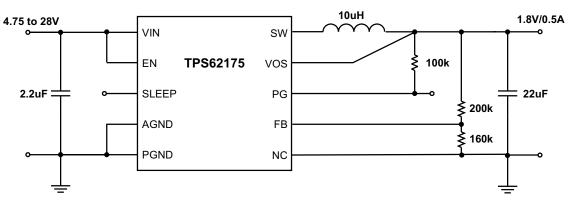

# TPS62175, TPS62177

#### ZHCSAD2A-OCTOBER 2012-REVISED NOVEMBER 2012

TEXAS INSTRUMENTS

www.ti.com.cn

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## **ORDERING INFORMATION**<sup>(1)(2)</sup>

| T <sub>A</sub> | OUTPUT VOLTAGE <sup>(2)</sup> | PART NUMBER | PACKAGE     | ORDERING    | PACKAGE<br>MARKING |

|----------------|-------------------------------|-------------|-------------|-------------|--------------------|

| -40°C to 85°C  | adjustable                    | TPS62175    | 10-Pin WSON | TPS62175DQC | 62175              |

|                | 3.3 V                         | TPS62177    | 10-PIN W30N | TPS62177DQC | 62177              |

(1) For detailed ordering information please check the PACKAGE OPTION ADDENDUM section at the end of this datasheet.

(2) Contact the factory to check availability of other output voltage or current limit versions.

## **ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>**

|                                     |                                                | MIN  | MAX                  | UNIT |

|-------------------------------------|------------------------------------------------|------|----------------------|------|

| Pin Voltage<br>Range <sup>(2)</sup> | VIN                                            | -0.3 | 30                   | V    |

|                                     | EN, SW                                         | -0.3 | V <sub>IN</sub> +0.3 | V    |

| rango                               | FB, PG, VOS, SLEEP, NC                         | -0.3 | 7                    | V    |

| Power Good Sink<br>Current          | PG                                             |      | 10                   | mA   |

| Temperature                         | Operating junction temperature, T <sub>J</sub> | -40  | 125                  | °C   |

| Range                               | Storage temperature, T <sub>stg</sub>          | -65  | 150                  |      |

| ESD rating <sup>(3)</sup>           | HBM Human body model                           |      | 2                    | kV   |

|                                     | CDM Charge device model                        |      | 0.5                  | kV   |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods my affect device reliability.

(2) All voltages are with respect to network ground terminal.

(3) ESD testing is performed according to the respective JESD22 JEDEC standard.

## THERMAL INFORMATION

|                              | THERMAL METRIC <sup>(1)</sup>                | TPS62175/7    |       |

|------------------------------|----------------------------------------------|---------------|-------|

|                              |                                              | DQC (10) PINS | UNITS |

| θ <sub>JA</sub>              | Junction-to-ambient thermal resistance       | 61.6          |       |

| $\theta_{JC(TOP)}$           | Junction-to-case(top) thermal resistance     | 65.5          |       |

| $\theta_{JB}$                | Junction-to-board thermal resistance         | 22.5          | °C/W  |

| Ψυτ                          | Junction-to-top characterization parameter   | 1.4           | C/W   |

| Ψ <sub>JB</sub>              | Junction-to-board characterization parameter | 22.4          |       |

| $\theta_{\text{JC(BOTTOM)}}$ | Junction-to-case(bottom) thermal resistance  | 5.3           |       |

#### (1) 有关传统和新的热度量的更多信息,请参阅/C 封装热度量应用报告, SPRA953。

## **RECOMMENDED OPERATING CONDITIONS**

|                                                | MIN  | MAX | UNIT |

|------------------------------------------------|------|-----|------|

| Supply Voltage, V <sub>IN</sub>                | 4.75 | 28  | V    |

| Operating free air temperature, T <sub>A</sub> | -40  | 85  | °C   |

| Operating junction temperature, T <sub>J</sub> | -40  | 125 | °C   |

www.ti.com.cn

## **ELECTRICAL CHARACTERISTICS**

over free-air temperature range ( $T_A$ =-40°C to +85°C) and  $V_{IN}$ =4.75 to 28V. Typical values at  $V_{IN}$ =12V and  $T_A$ =25°C (unless otherwise noted)

|                        | PARAMETER                                            | TEST CONDITIONS                                                  | MIN  | TYP  | MAX  | UNIT |

|------------------------|------------------------------------------------------|------------------------------------------------------------------|------|------|------|------|

| SUPPLY                 |                                                      |                                                                  | ÷    |      |      |      |

| V <sub>IN</sub>        | Input Voltage Range                                  |                                                                  | 4.75 |      | 28   | V    |

| l <sub>Q</sub>         | Operating Quiescent<br>Current                       | EN=High, SLEEP=High, I <sub>OUT</sub> =0mA, device not switching |      | 22   | 36   | μA   |

| I <sub>Q_SLEEP</sub>   | Sleep Mode Quiescent<br>Current                      | EN=High, SLEEP=Low, I <sub>OUT</sub> =0mA, device not switching  |      | 4.8  | 10   | μΑ   |

| I <sub>SD</sub>        | Shutdown Current                                     | EN=Low, current into VIN pin                                     |      | 1.5  | 5    | μA   |

| V <sub>UVLO</sub>      | Undervoltage Lockout                                 | Rising Input Voltage                                             | 4.5  | 4.6  | 4.7  | V    |

|                        | Threshold                                            | Falling Input Voltage                                            |      | 2.9  |      | V    |

| T <sub>SD</sub>        | Thermal Shutdown<br>Temperature                      | Rising Junction Temperature                                      |      | 150  |      | °C   |

|                        | Thermal Shutdown<br>Hysteresis                       |                                                                  |      | 20   |      |      |

| CONTROL                | (EN, PG, SLEEP)                                      |                                                                  |      |      |      |      |

| V <sub>H</sub>         | High Level Input<br>Threshold Voltage (EN,<br>SLEEP) |                                                                  | 0.9  |      |      | V    |

| VL                     | Low Level Input<br>Threshold Voltage (EN,<br>SLEEP)  |                                                                  |      |      | 0.3  | V    |

| I <sub>LKG_EN</sub>    | Input Leakage Current (EN)                           | EN=V <sub>IN</sub>                                               |      | 5    | 300  | nA   |

| I <sub>LKG_SLEEP</sub> | Input Leakage Current (SLEEP)                        | $V_{SLEEP} = 3.3V$                                               |      | 1.4  |      | μA   |

| V                      | Power Good Threshold                                 | Rising (%V <sub>OUT</sub> )                                      | 93   | 96   | 99   | %    |

| V <sub>TH_PG</sub>     | Voltage                                              | Falling (%V <sub>OUT</sub> )                                     | 87   | 90   | 93   | 70   |

| V <sub>OL_PG</sub>     | Power Good Output<br>Low Voltage                     | I <sub>PG</sub> = -2mA                                           |      |      | 0.3  | V    |

| I <sub>LKG_PG</sub>    | Input Leakage Current (PG)                           | V <sub>PG</sub> = 5V                                             |      | 5    | 300  | nA   |

| POWER SW               | /ІТСН                                                |                                                                  |      |      |      |      |

| Р                      | High-Side MOSFET<br>ON-Resistance                    | $V_{IN} \ge 6V$                                                  |      | 850  | 1430 | mΩ   |

| R <sub>DS(ON)</sub>    | Low-Side MOSFET<br>ON-Resistance                     | $V_{IN} \ge 6V$                                                  |      | 320  | 530  | mΩ   |

| l <b></b>              | High-Side MOSFET                                     | Normal Operation                                                 | 800  | 1000 | 1200 | mA   |

| LIMF                   | Current Limit                                        | Startup Mode                                                     | 450  | 525  | 600  | ШA   |

| OUTPUT                 |                                                      |                                                                  |      |      |      |      |

| V <sub>OUT</sub>       | Output Voltage Range<br>(TPS62175)                   | $V_{IN} \ge V_{OUT}$                                             | 1    |      | 6    | V    |

| V <sub>REF</sub>       | Internal Reference<br>Voltage                        |                                                                  |      | 0.8  |      | V    |

| I <sub>OUT_SLEEP</sub> | Output Current in Sleep<br>Mode                      | SLEEP= Low, V <sub>OUT</sub> =3.3V, L=10µH                       | 15   |      |      | mA   |

| I <sub>LKG_FB</sub>    | Input Leakage Current<br>(FB)                        | V <sub>FB</sub> = 0.8V                                           |      | 1    | 100  | nA   |

ZHCSAD2A-OCTOBER 2012-REVISED NOVEMBER 2012

## **ELECTRICAL CHARACTERISTICS (continued)**

over free-air temperature range ( $T_A$ =-40°C to +85°C) and  $V_{IN}$ =4.75 to 28V. Typical values at  $V_{IN}$ =12V and  $T_A$ =25°C (unless otherwise noted)

|                  | PARAMETER                                 |                                                                                                                                 | TEST CONDITIONS            |                                                    |      | TYP   | MAX | UNIT |

|------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------|------|-------|-----|------|

|                  |                                           | TPS62175 (adjustable                                                                                                            | PWM Mode                   |                                                    | -1.8 |       | 1.8 |      |

|                  |                                           | Vout), V <sub>IN</sub> ≥ V <sub>OUT</sub> +1V                                                                                   | Power Save Mode,<br>L=10µH | V <sub>OUT</sub> ≥ 2.5V,<br>C <sub>OUT</sub> =22µF | -1.8 |       | 3   |      |

|                  |                                           |                                                                                                                                 |                            | V <sub>OUT</sub> < 2.5V,<br>C <sub>OUT</sub> =44µF | -1.8 |       | 3.7 |      |

|                  | Output Voltage<br>Accuracy <sup>(1)</sup> | Sleep Mode, C <sub>OUT</sub> =22µF,<br>I <sub>OUT</sub> ≤15mA L=10µH                                                            |                            | -1.6                                               |      | 2.9   | %   |      |

| V <sub>OUT</sub> |                                           | TPS62177 (3.3V fixed<br>Vout) PWM Mode   Power Save Mode, C <sub>OUT</sub> =22µ   Sleep Mode, L=10µH   I <sub>OUT</sub> ≤15mA L | PWM Mode                   |                                                    | -2   |       | 2   |      |

|                  |                                           |                                                                                                                                 | C <sub>OUT</sub> =22µF,    | -2                                                 |      | 2.9   |     |      |

|                  |                                           |                                                                                                                                 |                            |                                                    | -1.6 |       | 2.7 |      |

|                  | Output Discharge<br>Resistance            | EN=Low                                                                                                                          |                            |                                                    |      | 175   |     | Ω    |

|                  | Load Regulation                           | V <sub>OUT</sub> =3.3V, PWM mode                                                                                                | operation                  |                                                    |      | 0.02  |     | %/A  |

|                  | Line Regulation                           | V <sub>OUT</sub> =3.3V, I <sub>OUT</sub> = 500m                                                                                 | A, PWM mode operation      | on                                                 |      | 0.015 |     | %/V  |

(1) The output voltage accuracy in Power Save and Sleep Mode can be improved by increasing the output capacitor value, reducing the output voltage ripple (see APPLICATION INFORMATION section).

#### ZHCSAD2A-OCTOBER 2012-REVISED NOVEMBER 2012

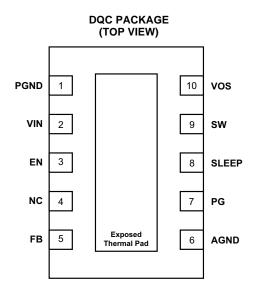

## **DEVICE INFORMATION**

### **TERMINAL FUNCTIONS**

| PIN                    | PIN <sup>(1)</sup> |     | PIN <sup>(1)</sup>                                                                                                                                                                  |  | DECODIDION |  |  |

|------------------------|--------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|------------|--|--|

| NAME                   | NO.                | I/O | DESCRIPTION                                                                                                                                                                         |  |            |  |  |

| PGND                   | 1                  |     | Power ground connection.                                                                                                                                                            |  |            |  |  |

| VIN                    | 2                  | I   | Supply voltage for the converter.                                                                                                                                                   |  |            |  |  |

| EN                     | 3                  | I   | Enable input (High=Enabled, Low= Disabled)                                                                                                                                          |  |            |  |  |

| NC                     | 4                  |     | This pin is recommended to be connected to AGND but can left be floating.                                                                                                           |  |            |  |  |

| FB                     | 5                  | I   | Voltage feedback of adjustable version. Connect resistive divider to this pin. It is recommended to connect FB to AGND for fixed voltage versions for improved thermal performance. |  |            |  |  |

| AGND                   | 6                  |     | Analog ground connection.                                                                                                                                                           |  |            |  |  |

| PG                     | 7                  | 0   | Output power good. (open drain, requires pull-up resistor)                                                                                                                          |  |            |  |  |

| SLEEP                  | 8                  | I   | Sleep mode input (High=Normal Operation, Low=Sleep mode Operation). Can be operated dynamically during operation.                                                                   |  |            |  |  |

| SW                     | 9                  | 0   | Switch node, connected to the internal MOSFET switches. Connect inductor between SW and output capacitor.                                                                           |  |            |  |  |

| VOS                    | 10                 | I   | Output voltage sense pin and connection for the control loop circuitry.                                                                                                             |  |            |  |  |

| Exposed<br>Thermal Pad |                    |     | Must be connected to AGND and PGND. Must be soldered to achieve appropriate power dissipation and mechanical reliability.                                                           |  |            |  |  |

(1) For more information about connecting pins, see DETAILED DESCRIPTION and APPLICATION INFORMATION sections.

TEXAS INSTRUMENTS

## ZHCSAD2A-OCTOBER 2012-REVISED NOVEMBER 2012

www.ti.com.cn

Figure 2. TPS62175 (adjustable output voltage)

ZHCSAD2A-OCTOBER 2012-REVISED NOVEMBER 2012

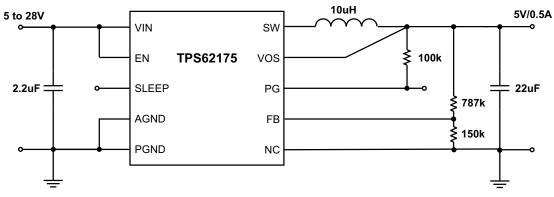

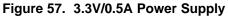

Figure 3. TPS62177 (fixed output voltage)

www.ti.com.cn

## PARAMETER MEASUREMENT INFORMATION

### **List of Components**

| REFERENCE | DESCRIPTION                         | MANUFACTURER                   |

|-----------|-------------------------------------|--------------------------------|

| IC        | 28V, 0.5A Step-Down Converter, WSON | TPS62175DQC, Texas Instruments |

| L1        | 10uH, (4 x 4 x 1.2) mm              | LPS4012, Coilcraft             |

| Cin       | 2.2µF, 50V, Ceramic, 0805, X5R      | Standard                       |

| Cout      | 22µF, 6.3V, Ceramic, 0805, X5R      | Standard                       |

| R1        | depending on Vout                   |                                |

| R2        | depending on Vout                   |                                |

| R3        | 100kΩ, Chip, 0603, 1/16W, 1%        | Standard                       |

Figure 4. Measurement Setup

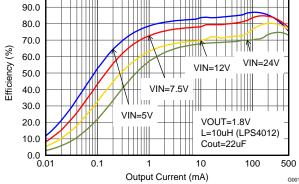

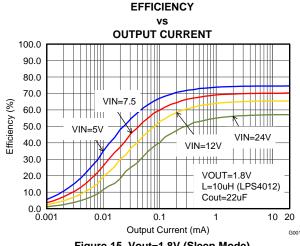

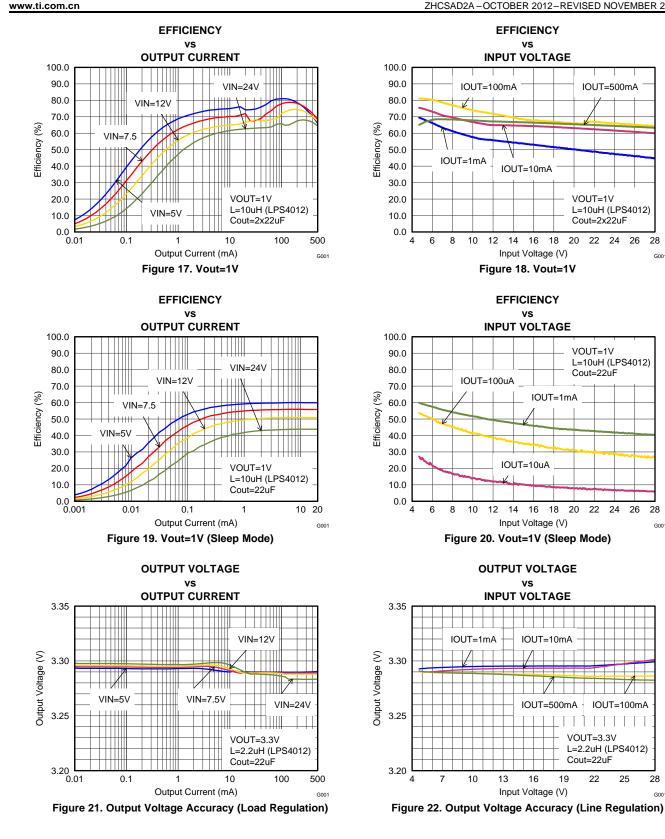

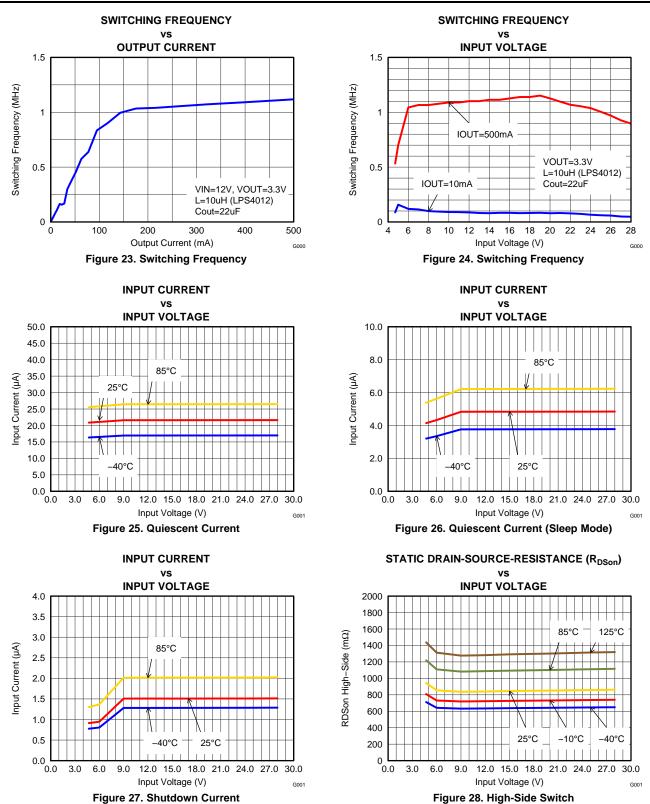

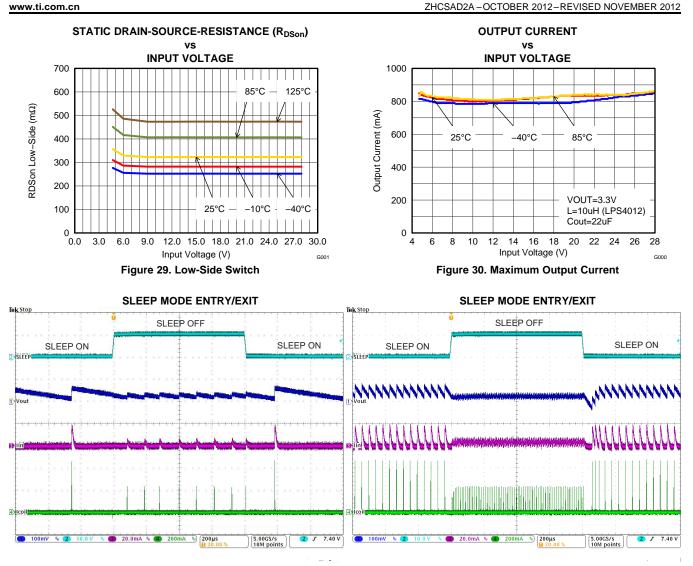

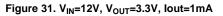

## **TYPICAL CHARACTERISTICS**

#### **Table of Graphs**

|                        | DESCRIPTION                                                              | FIGURE  |

|------------------------|--------------------------------------------------------------------------|---------|

| Efficiency             | vs Output Current, vs Input Voltage                                      | 5 - 20  |

| Output up have         | vs Output current (Load regulation)                                      | 21      |

| Output voltage         | vs Input Voltage (Line regulation)                                       | 22      |

|                        | vs Input Voltage                                                         | 23      |

| Switching Frequency    | vs Output Current                                                        | 24      |

| Quiescent Current      | vs Input Voltage                                                         | 25, 26  |

| Shutdown Current       | vs Input Voltage                                                         | 27      |

| Power FET RDS(on)      | vs Input Voltage (High-Side, Low-Side)                                   | 28, 29  |

| Maximum Output Current | vs Input Voltage                                                         | 30      |

|                        | Sleep Mode Transition                                                    | 31, 32  |

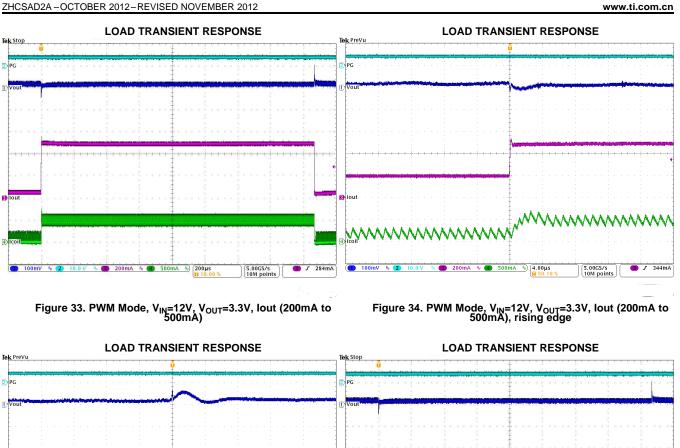

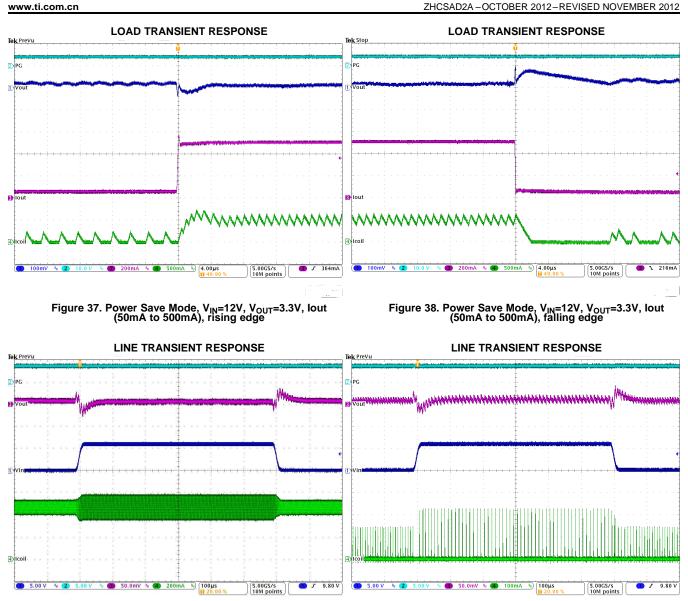

|                        | Load Transient Response                                                  | 33 - 38 |

|                        | Line Transient Response                                                  | 39, 40  |

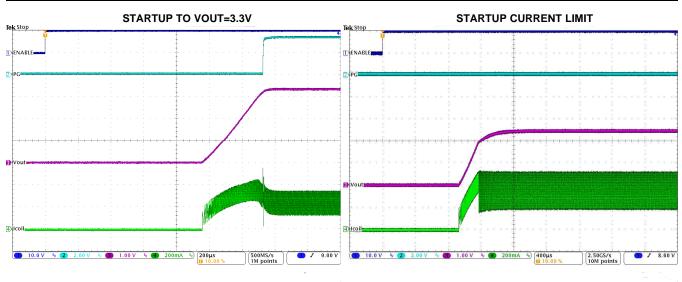

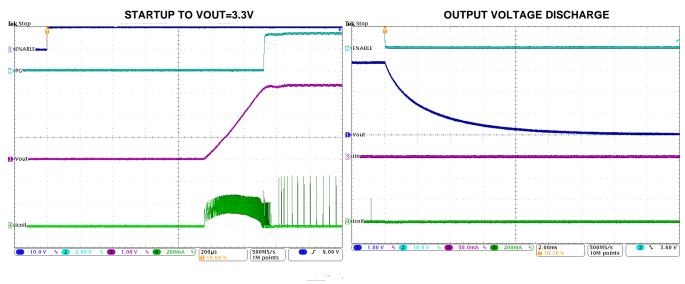

| Waveforms              | Startup                                                                  | 41 - 43 |

| Wavelonns              | Output Discharge                                                         | 44      |

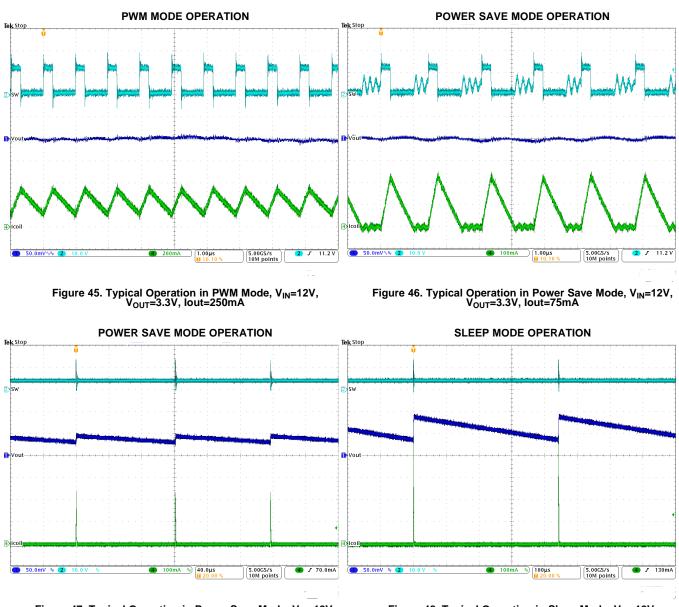

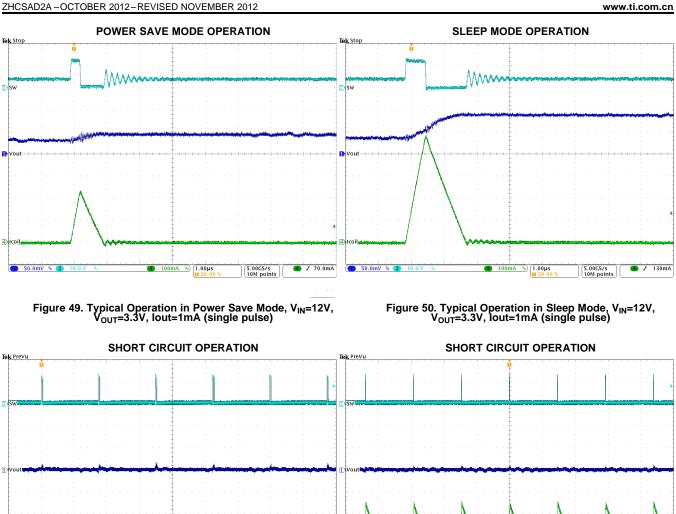

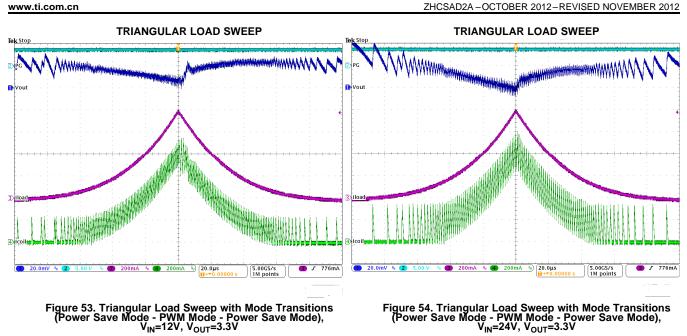

|                        | Typical Operation (PWM Mode, Power Save Mode, Sleep Mode, Short Circuit) | 45 - 52 |

|                        | Triangular Load Sweep with Mode Transitions                              | 53, 54  |

www.ti.com.cn

Figure 10. Vout=3.3V

100.0

#### ZHCSAD2A-OCTOBER 2012-REVISED NOVEMBER 2012

Figure 13. Vout=1.8V

www.ti.com.cn

**ISTRUMENTS**

EXAS

GOO

G001

#### ZHCSAD2A-OCTOBER 2012-REVISED NOVEMBER 2012

G00<sup>-</sup>

www.ti.com.cn

Figure 32. V<sub>IN</sub>=12V, V<sub>OUT</sub>=3.3V, Iout=10mA

# TPS62175, TPS62177

Æ

### ZHCSAD2A-OCTOBER 2012-REVISED NOVEMBER 2012

lout

100m\

$\sim$

5.00GS/s 10M points

Figure 35. PWM Mode,  $V_{\rm IN}{=}12V,~V_{\rm OUT}{=}3.3V,$  lout (200mA to 500mA), falling edge

4) 500mA 🍕

3 200mA

4.00µs

Figure 36. Power Save Mode, V<sub>IN</sub>=12V, V<sub>OUT</sub>=3.3V, lout (50mA to 500mA)

N 3 200mA N 4 500mA N 200µs 10.0

3 ∫ 284mA

5.00GS/s 10M points

Figure 39. PWM Mode, V<sub>IN</sub> (6V to 12V), lout=500mA

Figure 40. Power Save Mode, V<sub>IN</sub> (6V to 12V), lout=10mA

# TPS62175, TPS62177

#### ZHCSAD2A-OCTOBER 2012-REVISED NOVEMBER 2012

www.ti.com.cn

Figure 41. PWM Mode, V<sub>IN</sub>=12V, Iout=250mA

Figure 42. Startup Current Limit,  $V_{IN}$ =12V, Rload=6.6 $\Omega$

Figure 43. Sleep Mode, VIN=12V, lout=10mA

Figure 44. Output Discharge Function (Vout=3.3V, no load)

ZHCSAD2A-OCTOBER 2012-REVISED NOVEMBER 2012

Figure 47. Typical Operation in Power Save Mode,  $V_{\text{IN}}\text{=}12V, \\ V_{\text{OUT}}\text{=}3.3V, \text{ lout}\text{=}1\text{mA}$

Figure 48. Typical Operation in Sleep Mode, V\_{IN}=12V, V\_{OUT}=3.3V, lout=1mA

# TPS62175, TPS62177

4

1

#### ZHCSAD2A-OCTOBER 2012-REVISED NOVEMBER 2012

2 J 8.20 V

🚺 100mV 🗞 🔁 10.0 V

(**1** 100mV % **2** 10.0 500mA

10.0µs

10.1 5.00GS/s 10M points

Figure 51. Short circuit while running, VIN=12V

Figure 52. Short circuit from startup, V<sub>IN</sub>=12V

5.00GS/s 10M points

2 J 8.20 V

## DETAILED DESCRIPTION

## **Device Operation**

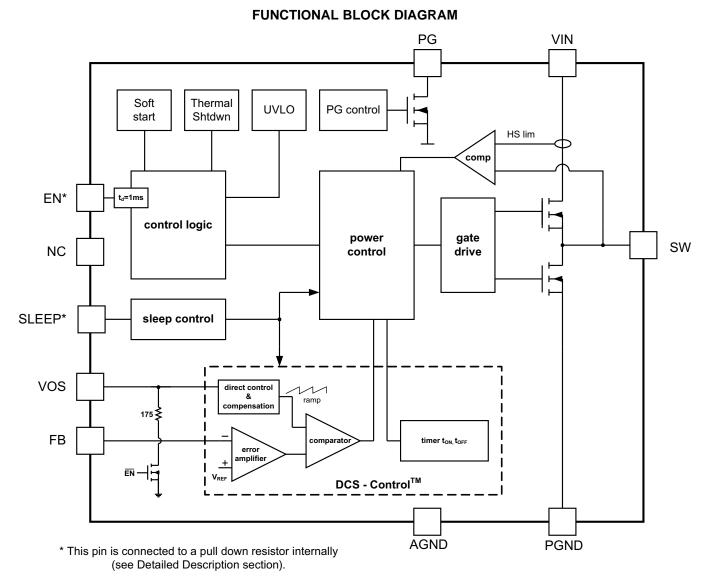

The TPS62175/7 synchronous switch mode power converters are based on DCS-Control<sup>™</sup> (**D**irect **C**ontrol with **S**eamless Transition into Power Save Mode), an advanced regulation topology, that combines the advantages of hysteretic, voltage mode and current mode control including an AC loop directly associated to the output voltage. This control loop takes information about output voltage changes and feeds it directly to a fast comparator stage. It sets the switching frequency, which is constant for steady state operating conditions, and provides immediate response to dynamic load changes. To get accurate DC load regulation, a voltage feedback loop is used. The internally compensated regulation network achieves fast and stable operation with small external components and low ESR capacitors.

The DCS-Control<sup>™</sup> topology supports PWM (Pulse Width Modulation) mode for medium and heavy load conditions and a Power Save Mode at light loads. During PWM, it operates at its nominal switching frequency in continuous conduction mode. This frequency is typically about 1MHz with a controlled frequency variation depending on the input voltage. If the load current decreases, the converter enters Power Save Mode to sustain high efficiency down to very light loads. In Power Save Mode the switching frequency decreases linearly with the load current. Since DCS-Control<sup>™</sup> supports both operation modes within one single building block, the transition from PWM to Power Save Mode is seamless without effects on the output voltage. Fixed output voltage versions provide smallest solution size and lowest current consumption, requiring only 3 external components. An internal current limit supports nominal output currents of up to 500mA. The TPS62175/7 offer both excellent DC voltage and superior load transient regulation, combined with very low output voltage ripple, minimizing interference with RF circuits.

## Pulse Width Modulation (PWM) Operation

The TPS62175/7 operates with pulse width modulation in continuous conduction mode (CCM) with a nominal switching frequency of about 1MHz. The switching frequency in PWM is set by an internal timer circuit. The frequency variation is controlled and depends on  $V_{IN}$  and  $V_{OUT}$ . The device operates in PWM mode as long the output current is higher than half the inductor's ripple current. To maintain high efficiency at light loads, the device enters Power Save Mode at the boundary to discontinuous conduction mode (DCM).

## Power Save Mode Operation

The TPS62175/7's built in Power Save Mode is entered seamlessly, if the load current decreases. This secures a high efficiency in light load operation by keeping the on-time and reducing the switching frequency. The device remains in Power Save Mode as long as the inductor current is discontinuous. The on-time, in steady-state operation, can be estimated as:

$$t_{ON} = \frac{V_{OUT}}{V_{IN}} \cdot 1\mu s \tag{1}$$

While the peak inductor current in Power Save Mode can be approximated by:

$$I_{LPSM(peak)} = \frac{(V_{IN} - V_{OUT})}{L} \cdot t_{ON}$$

The switching frequency is calculated as follows:

$\mathbf{V}$

١

20

(V

www.ti.com.cn

(י)

(2)

(3)

#### www.ti.com.cn

#### **Sleep Mode Operation**

In Sleep Mode operation, the typical quiescent current is reduced from  $22\mu$ A to  $4.8\mu$ A to significantly increase the efficiency at load currents of typically less than 1mA (see  $\mathbb{R}$  1). The output voltage is regulated with a fixed on-time, which is adjusted according to V<sub>IN</sub>. A new pulse is initiated once the output voltage falls below its regulation threshold. Sleep Mode is limited with its dynamic response and current capabilities. It is designed to be enabled and disabled by pulling the SLEEP pin High or Low.

As a safety feature, the device returns to normal operation automatically, if too much current is drawn, avoiding a complete collapse of Vout. Once the load current decreases again, the device re-enters Sleep mode operation. However, this is not a recommended operation mode.

Ultra low power micro controllers in deep sleep or hibernating mode might have floating output pins. Therefore, TPS62175/7 have a pull-down resistor internally connected to the Sleep pin, to keep a logic low level, when the Sleep input signal goes High Impedance. If the Sleep signal goes directly from logic High to High Impedance, the low level detection must be ensured considering the leakage of the micro controller's Sleep signal. An external pull-down resistor, shown in Figure 62, may be required. The device can deliver temporarily more than 15mA, to allow micro controllers to wake up and drive the Sleep signal High, exiting Sleep Mode.

#### **100% Mode Operation**

The duty cycle of the buck converter is given by D=Vout/Vin and increases as the input voltage comes close to the output voltage. In this case, the device starts 100% duty cycle operation turning on the high-side switch 100% of the time. The high-side switch stays turned on as long as the output voltage is below the internal setpoint. This allows the conversion of small input to output voltage differences, e.g. for longest operation time of battery-powered applications.

The minimum input voltage to maintain output voltage regulation can be calculated as:

$$V_{IN(min)} = V_{OUT(min)} + I_{OUT} \left( R_{DS(on)} + R_L \right)$$

where

$I_{OUT}$  is the output current,  $R_{DS(on)}$  is the  $R_{DS(on)}$  of the high-side FET and  $R_L$  is the DC resistance of the inductor used.

#### Enable/Shutdown (EN)

The device can be switched on/off by pulling the EN pin to High (operation) or Low (shutdown). If EN is pulled to High, the device starts operation after a delay of about 1ms (typ.). This helps to ensure a monotonic startup sequence, which makes the device ideally suited to control the power on sequence of micro controllers.

During Shutdown, the internal MOSFETs as well as the entire control circuitry are turned off and the current consumption is typically 1.5 $\mu$ A. The EN pin is connected via a 400k $\Omega$  pull-down resistor, keeping the logic level low, if the pin is floating.

#### **Output Discharge**

The output is actively discharged through a  $175\Omega$  (typ.) resistor on the VOS pin when the device is turned off by EN, UVLO or thermal shutdown.

(4)

www.ti.com.cn

## Softstart

The internal soft start circuitry controls the output voltage slope during startup. This avoids excessive inrush current and ensures a controlled output voltage rise time. It also prevents unwanted voltage drops from high-impedance power sources or batteries. When EN is set to High and the device starts switching,  $V_{OUT}$  rises with a slope of typically 10mV/µs. The internal current limit is reduced to typically 525mA during startup. Thereby the output current is less than 500mA during hat time (see Figure 42). The startup sequence ends, when device achieves regulation, then, the device runs with the full current limit of typically 1A, providing full output current.

The TPS62175/7 can monotonically start into a pre-biased output.

## **Current Limit And Short Circuit Protection**

The TPS62175/7 devices are protected against heavy load and short circuit events. If a current limit situation is detected, the device switches off. The off time is maintained longer as the output voltage becomes lower. At heavy overloads the low side MOSFET stays on until the inductor current returns to zero. Then the high side MOSFET turns on again (see Figure 51 and Figure 52).

## Power Good (PG)

The TPS62175/7 has a built in power good (PG) function to indicate that the output reached regulation. The PG signal can be used for startup sequencing of multiple rails. The PG pin is an open-drain output that requires a pull-up resistor (to any voltage below 7V). It can sink 2mA of current and maintain its specified logic Low level of 0.3V. It is held Low when the device is turned off by EN, UVLO or thermal shutdown.

If the PG pin is not used, it may be left floating or connected to AGND.

## Under Voltage Lockout (UVLO)

If the input voltage drops, the under voltage lockout function prevents misoperation by turning the device off. The under voltage lockout threshold is set to 4.6V (typically) for rising  $V_{IN}$ . To cover for possible input voltage drops, when using high impedance sources or batteries, the falling threshold is set to typically 2.9V, allowing monotonic startup sequence under such conditions. For input voltages below the minimum VIN of 4.75V and above the falling UVLO threshold of 2.9V, the device still functions with a current limit and regulation capability but the electrical characteristics are no longer specified.

## **Thermal Shutdown**

The junction temperature (Tj) of the device is monitored by an internal temperature sensor. If Tj exceeds 150°C (typ), the device goes into thermal shutdown. Both the high-side and low-side power FETs are turned off and PG goes Low. When Tj decreases below the hysteresis amount, the converter resumes normal operation, beginning with Soft Start. To avoid unstable conditions, a hysteresis of typically 20°C is implemented on the thermal shutdown temperature.

ZHCSAD2A-OCTOBER 2012-REVISED NOVEMBER 2012

## **APPLICATION INFORMATION**

## Programming The Output Voltage

While the output voltage of the TPS62175 is adjustable, the TPS62177 is programmed to a fixed output voltage of 3.3V. For the fixed output voltage version, the FB pin is pulled low internally by a 400k $\Omega$  resistor. It is recommended to connect the FB pin to AGND to improve thermal resistance. The adjustable version can be programmed for output voltages from 1V to 6V by using a resistive divider. The voltage at the FB pin is regulated to 800mV. The value of the output voltage is set by the selection of the resistive divider from Equation 5. It is recommended to choose resistor values which allow a current of at least 5uA. Lower resistor values are recommended to increase noise immunity. For applications requiring lowest current consumption, the use of the fixed output voltage version is recommended.

$$R_1 = R_2 \quad \left(\frac{V_{OUT}}{V_{REF}} - 1\right) \tag{5}$$

As a safety feature, the device clamps the output voltage at the VOS pin to typically 7.4V, if the FB pin gets opened.

### **External Component Selection**

The external components have to fulfill the needs of the application, but also the stability criteria of the devices control loop. The TPS62175/7 is optimized to work within a wide range of external components. The LC output filter's inductance and capacitance have to be considered together, while creating a double pole that is responsible for the corner frequency of the converter. Table 1 shows the recommended output filter components.

|       | 10µF | 22µF             | 47µF         | 100µF        | 200µF        | 400µF |

|-------|------|------------------|--------------|--------------|--------------|-------|

| 6.8µH |      |                  |              |              |              |       |

| 10µH  |      | <sub>√</sub> (2) | $\checkmark$ | $\checkmark$ | $\checkmark$ |       |

| 22µH  |      |                  |              | $\checkmark$ | $\checkmark$ |       |

| 33µH  |      |                  |              |              |              |       |

Table 1. Recommended LC Output Filter Combinations<sup>(1)</sup>

(1) The values in the table are nominal values. Variations of typically ±20% due to tolerance, saturation and DC bias are assumed.

(2) This LC combination is the standard value and recommended for most applications. For output voltages of ≤2V, an output capacitance of at least 2x22uF is recommended.

#### **Output Filter And Loop Stability**

The TPS62175/7 devices are internally compensated and are stable with LC output filter combinations recommended in Table 1. Further information on other values and loop stability can be found in SLVA543.

#### **Inductor Selection**

The inductor selection is determined by several effects like inductor ripple current, output ripple voltage, PWM-to-Power Save Mode transition point and efficiency. In addition, the inductor selected has to be rated for appropriate saturation current and DC resistance (DCR). Equation 6 and Equation 7 calculate the maximum inductor current under static load conditions.

$$I_{\scriptscriptstyle L(\rm max)} = I_{\scriptscriptstyle OUT(\rm max)} + \frac{\Delta I_{\scriptscriptstyle L(\rm max)}}{2}$$

(6)

$$\Delta I_{L(\max)} = \frac{V_{OUT}}{\eta} \cdot \left( \frac{1 - \frac{V_{OUT}}{V_{IN(\max)} \cdot \eta}}{L_{(\min)} \cdot f_{SW}} \right)$$

where

$\Delta I_L$  is the Peak to Peak Inductor Ripple Current,

$\eta$  is the converter efficiency (see efficiency figures),

L(min) is the minimum inductor value and

f<sub>SW</sub> is the actual PWM Switching Frequency.

Calculating the maximum inductor current using the actual operating conditions gives the minimum saturation current of the inductor needed. A margin of about 20% is recommended to cover possible load transient overshoot. A larger inductor value is also useful to get lower ripple current, but increases the transient response time and solution size as well. The following inductors have been tested with the TPS62175/7:

| Туре              | Inductance [µH] | Current [A] <sup>(1)</sup> | DCR [mΩ]  | Dimensions [L x B x H]<br>mm | MANUFACTUR<br>ER |

|-------------------|-----------------|----------------------------|-----------|------------------------------|------------------|

| LPS4012-103MLC    | 10µH, ±20%      | 1.1A                       | 350 (max) | 4.0 x 4.0 x 1.2              | Coilcraft        |

| LPS4018-103MLC    | 10µH, ±20%      | 1.3A                       | 200 (max) | 4.0 x 4.0 x 1.8              | Coilcraft        |

| VLS4012ET-100M    | 10µH, ±20%      | 0.99A                      | 190 (typ) | 4.0 x 4.0 x 1.2              | TDK              |

| VLCF4020T-100MR85 | 10µH, ±20%      | 0.85A                      | 168 (typ) | 4.0 x 4.0 x 2.0              | TDK              |

| 74437324100       | 10µH, ±20%      | 1.5 A                      | 215 (typ) | 4.5 x 4.1 x 1.8              | Wuerth           |

| IFSC-1515AH-01    | 10µH, ±20%      | 1.3A                       | 135 (typ) | 3.8 x 3.8 x 1.8              | Vishay           |

| ELL-4LG100MA      | 10µH, ±20%      | 0.8A                       | 200 (typ) | 3.8 x 3.8 x 1.8              | Panasonic        |

Table 2. List of Inductors

(1)  $I_{RMS}$  at 40°C rise or  $I_{SAT}$  at 30% drop.

## **Output Capacitor**

The recommended value for the output capacitor is 22uF. To maintain low output voltage ripple during large load transients, for output voltages below 2V, 2x 22µF is recommended. The architecture of the TPS62175/7 allows the use of ceramic output capacitors with low equivalent series resistance (ESR). These capacitors provide low output voltage ripple and are recommended with an X7R or X5R dielectric. Larger capacitance values have the advantage of smaller output voltage ripple and a tighter DC output accuracy in Power Save Mode.

Note: In Power Save Mode, the output voltage ripple and accuracy depends on the output capacitance and the inductor value. The larger the capacitance the lower the output voltage ripple and the better the output voltage accuracy. The same relation applies to the inductor value.

## Input Capacitor

Typically, 2.2µF is sufficient and is recommended, though a larger value reduces input current ripple further. The input capacitor buffers the input voltage during transient events and also decouples the converter from the supply. A low ESR, multilayer, X5R or X7R dielectric, ceramic capacitor is recommended for best filtering and should be placed between VIN and PGND as close as possible to those pins.

## NOTE

**DC Bias effect:** High capacitance ceramic capacitors have a DC Bias effect, which has a strong influence on the final effective capacitance. Therefore the right capacitor value has to be chosen carefully. Package size and voltage rating in combination with dielectric material are responsible for differences between the rated capacitor value and the effective capacitance.

(7)

#### www.ti.com.cn

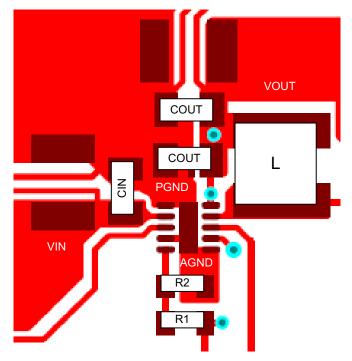

#### **Layout Considerations**

The input capacitor needs to be placed as close as possible to the IC pins (VIN, PGND). The inductor should be placed close to the SW pin and connect directly to the output capacitor - minimizing the loop area between the SW pin, inductor, output capacitor and PGND pin. Also, sensitive nodes like FB and VOS should be connected with short wires, not nearby high dv/dt signals (e.g. SW). The feedback resistors,  $R_1$  and  $R_2$ , should be placed close to the IC and connect directly to the AGND and FB pins.

A proper layout is critical for the operation of a switch mode power supply, even more at high switching frequencies. Therefore the PCB layout of the TPS62175/7 demands careful attention to ensure operation and to get the performance specified. A poor layout can lead to issues like poor regulation (both line and load), stability and accuracy weaknesses, increased EMI radiation and noise sensitivity. See Figure 55 for the recommended layout of the TPS62175, which is implemented on the EVM. Information can be found in the EVM Users Guide, SLVU743. Alternatively, the EVM Gerber data are available for download here, SLVC453.

Figure 55. Layout Example

The Exposed Thermal Pad must be soldered to AGND and on the circuit board for mechanical reliability and to achieve appropriate power dissipation.

#### THERMAL INFORMATION

The TPS62175/7 is designed for a maximum operating junction temperature  $(T_j)$  of 125°C. Therefore the maximum output power is limited by the power losses. Since the thermal resistance of the package is given, the size of the surrounding copper area and a proper thermal connection of the IC can reduce the thermal resistance. To get an improved thermal behavior, it's recommended to use top layer metal to connect the device with wide and thick metal lines (see Figure 55 above). Internal ground layers can connect to vias directly under the IC for improved thermal performance.

For more details on how to use the thermal parameters, see the application notes: Thermal Characteristics Application Note (SZZA017), and (SPRA953).

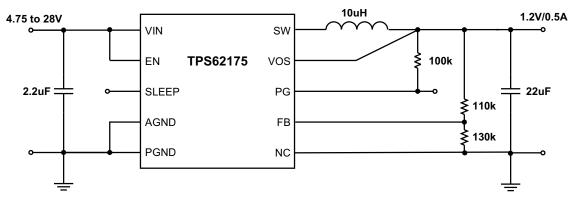

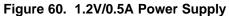

## **Typical Applications**

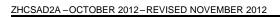

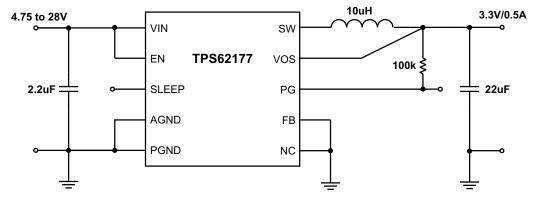

Figure 56. 5V/0.5A Power Supply

Figure 58. 2.5V/0.5A Power Supply

www.ti.com.cn

www.ti.com.cn

**NSTRUMENTS**

**FEXAS**

## **Application Examples**

## **Micro Controller Power Supply**

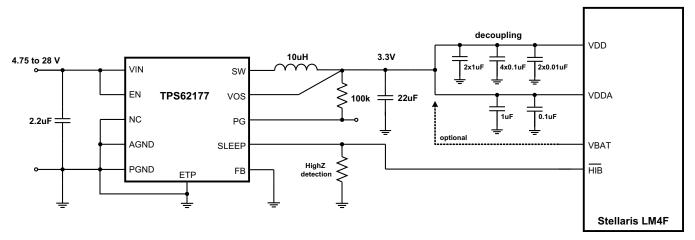

The TPS6215/7 can be used advantageously as the power supply rail for micro-controllers with low current power save modes. Figure 62 shows the connection of TPS62177 to the Stellaris Cortex M4 micro-controller (LM4F), using its Hibernate Mode signal to control Sleep Mode operation.

Figure 62. Micro-Controller Power Supply with Sleep Mode

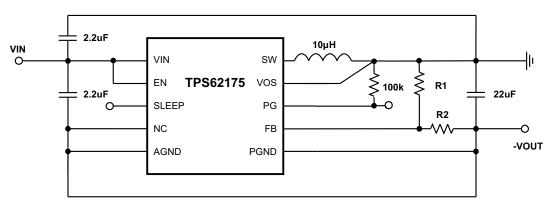

## **Inverting Power Supply**

The TPS62175/7 can be used as inverting power supply by rearranging external circuitry as shown in Figure 63. As the former GND node now represents a voltage level below system ground, the voltage difference between  $V_{IN}$  and  $V_{OUT}$  has to be limited to the maximum operating voltage of 28V.

Figure 63. Inverting Buck-Boost Converter

More information about using TPS62175 as inverting buck-boost converter can be found in the Application Note SLVA542.

ZHCSAD2A-OCTOBER 2012-REVISED NOVEMBER 2012

## **REVISION HISTORY**

| Cł | Changes from Original (October 2012) to Revision A                                 |    |  |  |  |  |

|----|------------------------------------------------------------------------------------|----|--|--|--|--|

| •  | Added Startup Mode to High-Side MOSFET Current Limit in ELECTRICAL CHARACTERISTICS | 3  |  |  |  |  |

| •  | Changed Table 1                                                                    | 23 |  |  |  |  |

## **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty |              | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing            |      | QLY            | (2)          | (6)                           | (3)                 |              | (4/5)          |         |

| TPS62175DQCR     | ACTIVE | WSON         | DQC                | 10   | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | 62175          | Samples |

| TPS62175DQCT     | ACTIVE | WSON         | DQC                | 10   | 250            | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | 62175          | Samples |

| TPS62177DQCR     | ACTIVE | WSON         | DQC                | 10   | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | 62177          | Samples |

| TPS62177DQCT     | ACTIVE | WSON         | DQC                | 10   | 250            | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | 62177          | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and

www.ti.com

10-Dec-2020

continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

Texas Instruments

www.ti.com

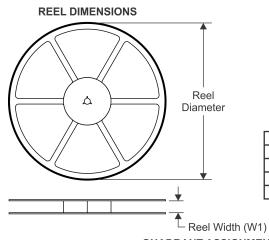

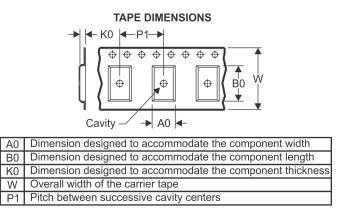

## TAPE AND REEL INFORMATION

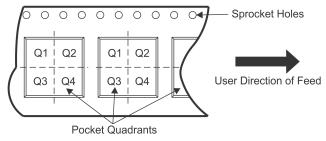

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| TPS62175DQCR                | WSON            | DQC                | 10 | 3000 | 180.0                    | 8.4                      | 2.25       | 3.25       | 1.05       | 4.0        | 8.0       | Q1               |

| TPS62175DQCR                | WSON            | DQC                | 10 | 3000 | 180.0                    | 8.4                      | 2.25       | 3.25       | 1.05       | 4.0        | 8.0       | Q1               |

| TPS62175DQCT                | WSON            | DQC                | 10 | 250  | 180.0                    | 8.4                      | 2.25       | 3.25       | 1.05       | 4.0        | 8.0       | Q1               |

| TPS62175DQCT                | WSON            | DQC                | 10 | 250  | 180.0                    | 8.4                      | 2.25       | 3.25       | 1.05       | 4.0        | 8.0       | Q1               |

| TPS62177DQCR                | WSON            | DQC                | 10 | 3000 | 180.0                    | 8.4                      | 2.25       | 3.25       | 1.05       | 4.0        | 8.0       | Q1               |

| TPS62177DQCR                | WSON            | DQC                | 10 | 3000 | 180.0                    | 8.4                      | 2.25       | 3.25       | 1.05       | 4.0        | 8.0       | Q1               |

| TPS62177DQCT                | WSON            | DQC                | 10 | 250  | 180.0                    | 8.4                      | 2.25       | 3.25       | 1.05       | 4.0        | 8.0       | Q1               |

| TPS62177DQCT                | WSON            | DQC                | 10 | 250  | 180.0                    | 8.4                      | 2.25       | 3.25       | 1.05       | 4.0        | 8.0       | Q1               |

www.ti.com

# PACKAGE MATERIALS INFORMATION

26-Jan-2022

| *All dimensions are nominal |              |                 |      |      |             |            |             |

|-----------------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| Device                      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

| TPS62175DQCR                | WSON         | DQC             | 10   | 3000 | 210.0       | 185.0      | 35.0        |

| TPS62175DQCR                | WSON         | DQC             | 10   | 3000 | 210.0       | 185.0      | 35.0        |

| TPS62175DQCT                | WSON         | DQC             | 10   | 250  | 210.0       | 185.0      | 35.0        |

| TPS62175DQCT                | WSON         | DQC             | 10   | 250  | 210.0       | 185.0      | 35.0        |

| TPS62177DQCR                | WSON         | DQC             | 10   | 3000 | 210.0       | 185.0      | 35.0        |

| TPS62177DQCR                | WSON         | DQC             | 10   | 3000 | 210.0       | 185.0      | 35.0        |

| TPS62177DQCT                | WSON         | DQC             | 10   | 250  | 210.0       | 185.0      | 35.0        |

| TPS62177DQCT                | WSON         | DQC             | 10   | 250  | 210.0       | 185.0      | 35.0        |

# **GENERIC PACKAGE VIEW**

# WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.