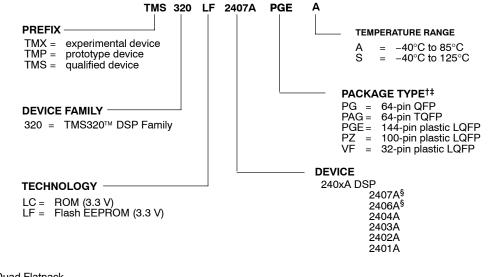

DSP CONTROLLERS SPRS145L - JULY 2000 - REVISED SEPTEMBER 2007

- High-Performance Static CMOS Technology - 25-ns Instruction Cycle Time (40 MHz)

- 40-MIPS Performance

- Low-Power 3.3-V Design

- Based on TMS320C2xx DSP CPU Core

- Code-Compatible With F243/F241/C242 Instruction Set and Module Compatible

- With F240

- Flash (LF) and ROM (LC) Device Options - LF240xA: LF2407A, LF2406A,

- LF2403A, LF2402A

- LC240xA: LC2406A, LC2404A, LC2403A, LC2402A

- **On-Chip Memory**

- Up to 32K Words x 16 Bits of Flash **EEPROM (4 Sectors) or ROM**

- Programmable "Code-Security" Feature for the On-Chip Flash/ROM

- Up to 2.5K Words x 16 Bits of **Data/Program RAM**

- 544 Words of Dual-Access RAM

- Up to 2K Words of Single-Access RAM

- Boot ROM (LF240xA Devices) - SCI/SPI Bootloader

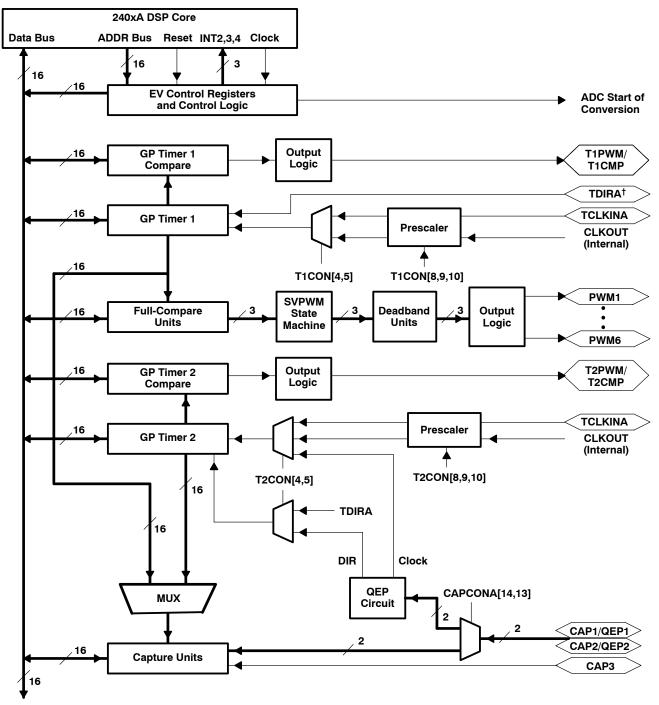

- Up to Two Event-Manager (EV) Modules (EVA and EVB), Each Includes:

- Two 16-Bit General-Purpose Timers

- Eight 16-Bit Pulse-Width Modulation (PWM) Channels Which Enable:

- Three-Phase Inverter Control

- Center- or Edge-Alignment of PWM Channels

- Emergency PWM Channel Shutdown With External PDPINTx Pin

- Programmable Deadband (Deadtime) **Prevents Shoot-Through Faults**

- Three Capture Units for Time-Stamping of External Events

- Input Qualifier for Select Pins

- On-Chip Position Encoder Interface Circuitry

- Synchronized A-to-D Conversion

- Designed for AC Induction, BLDC, Switched Reluctance, and Stepper Motor Control

- Applicable for Multiple Motor and/or **Converter Control**

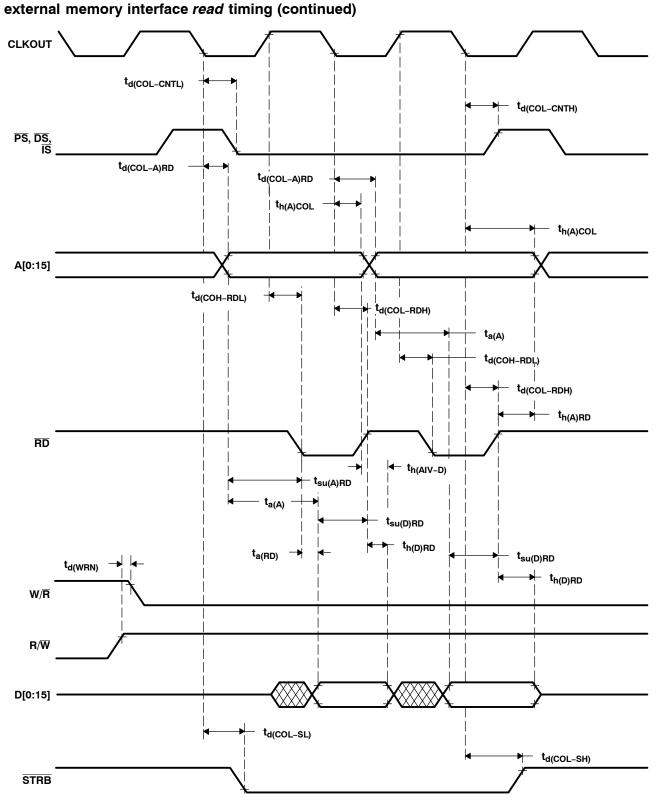

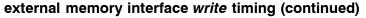

- External Memory Interface (LF2407A) - 192K Words x 16 Bits of Total Memory: 64K Program, 64K Data, 64K I/O

- Watchdog (WD) Timer Module

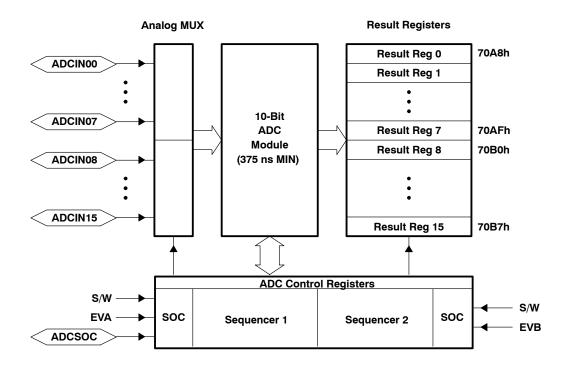

- 10-Bit Analog-to-Digital Converter (ADC) – 8 or 16 Multiplexed Input Channels

- 500-ns MIN Conversion Time

- Selectable Twin 8-State Sequencers Triggered by Two Event Managers

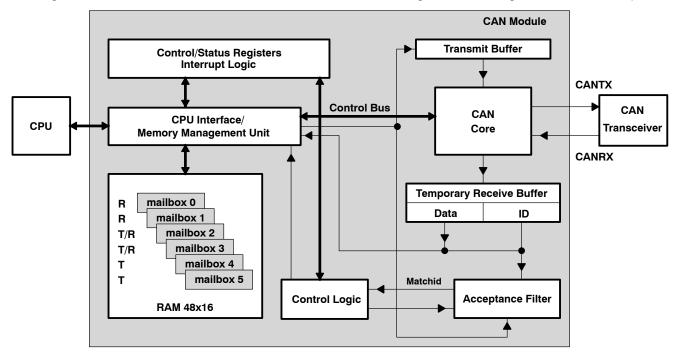

- **Controller Area Network (CAN) 2.0B Module** (LF2407A, 2406A, 2403A)

- Serial Communications Interface (SCI)

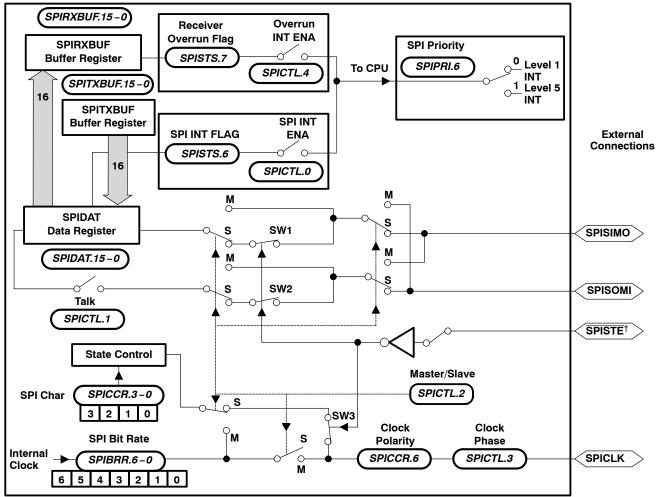

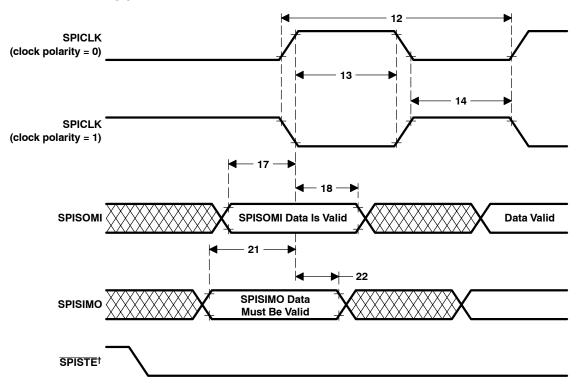

- **16-Bit Serial Peripheral Interface (SPI)** (LF2407A, 2406A, LC2404A, 2403A)

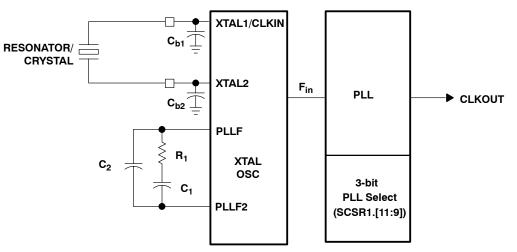

- Phase-Locked-Loop (PLL)-Based Clock Generation

- Up to 40 Individually Programmable, Multiplexed General-Purpose Input/Output (GPIO) Pins

- Up to Five External Interrupts (Power Drive Protection, Reset, Two Maskable Interrupts)

- **Power Management:**

- Three Power-Down Modes

- Ability to Power Down Each Peripheral Independently

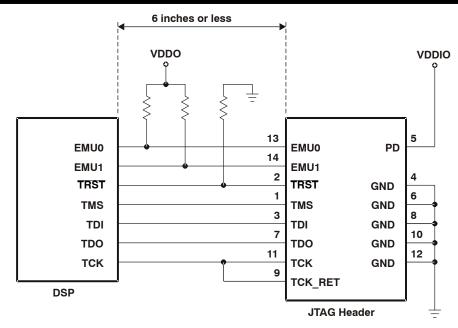

- **Real-Time JTAG-Compliant Scan-Based** Emulation, IEEE Standard 1149.1<sup>+</sup> (JTAG)

- **Development Tools Include:**

- Texas Instruments (TI) ANSI C Compiler, Assembler/Linker, and Code Composer Studio<sup>™</sup> Debugger

- Evaluation Modules

- Scan-Based Self-Emulation (XDS510<sup>™</sup>)

- Broad Third-Party Digital Motor Control Support

- Package Options

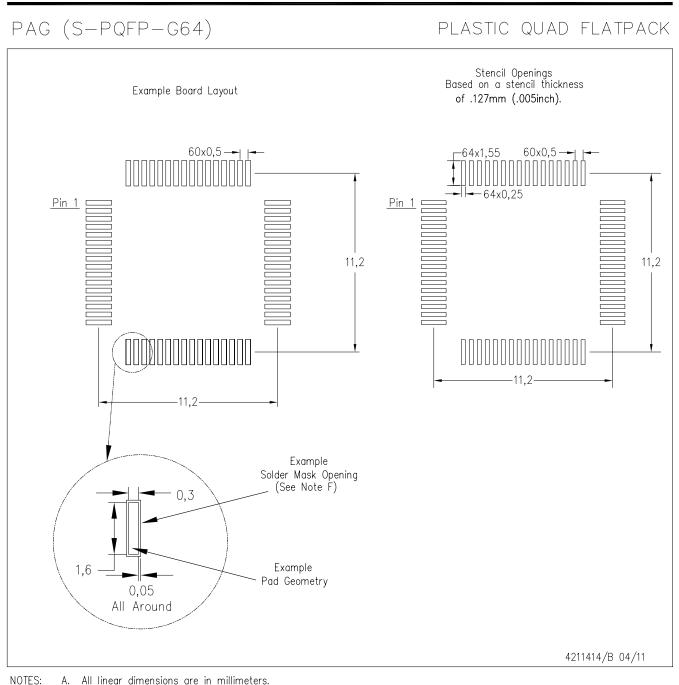

- 144-Pin LQFP PGE (LF2407A)

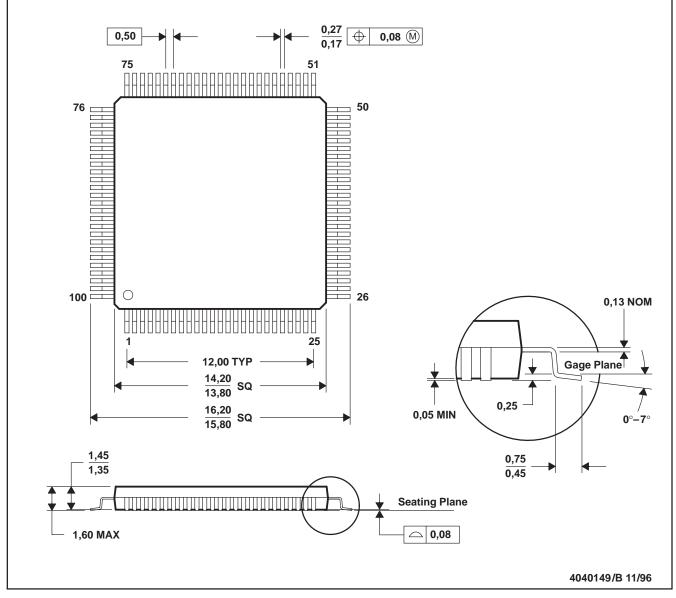

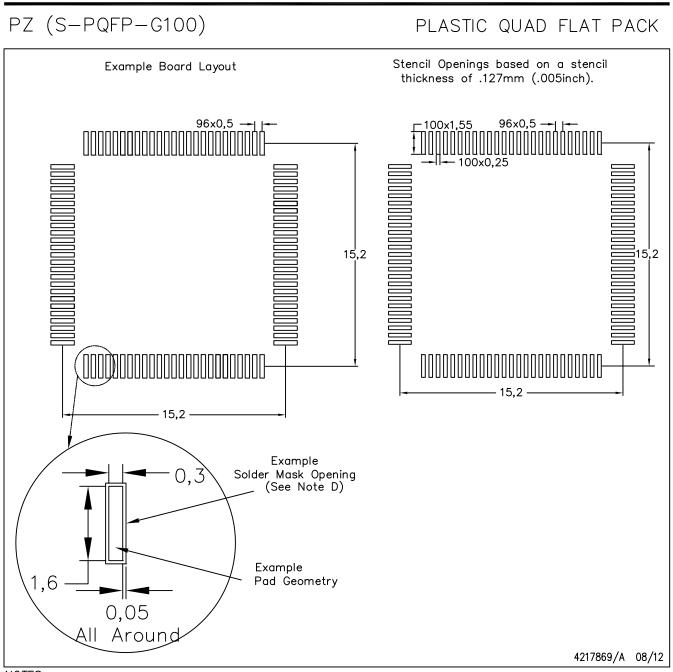

- 100-Pin LQFP PZ (2406A, LC2404A)

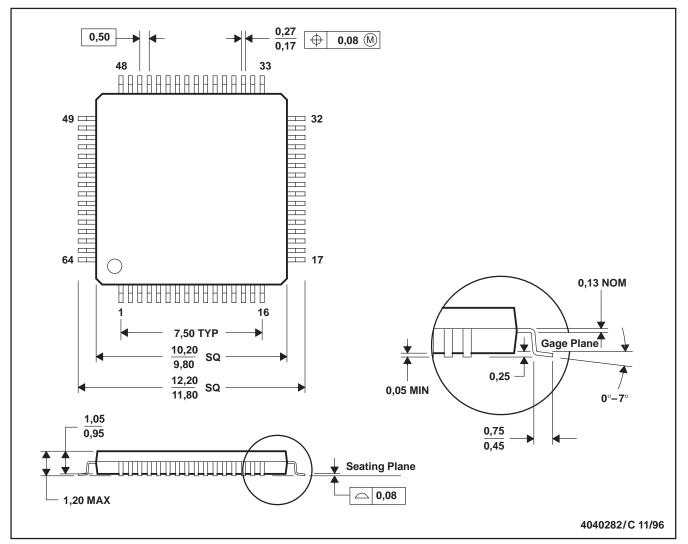

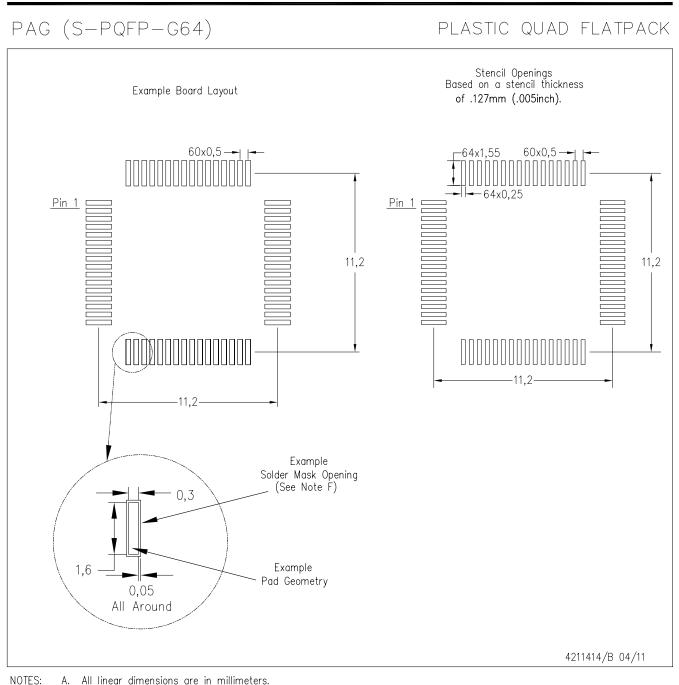

- 64-Pin TQFP PAG (LF2403A, LC2403A, LC2402A)

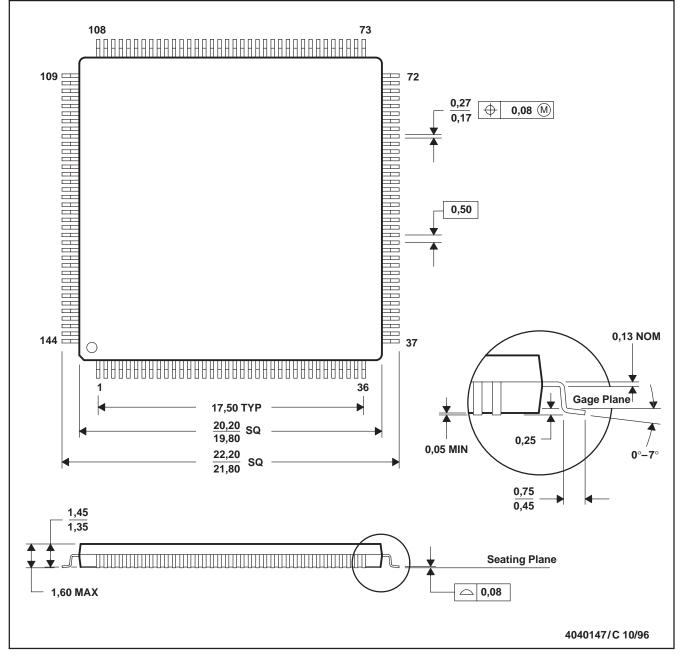

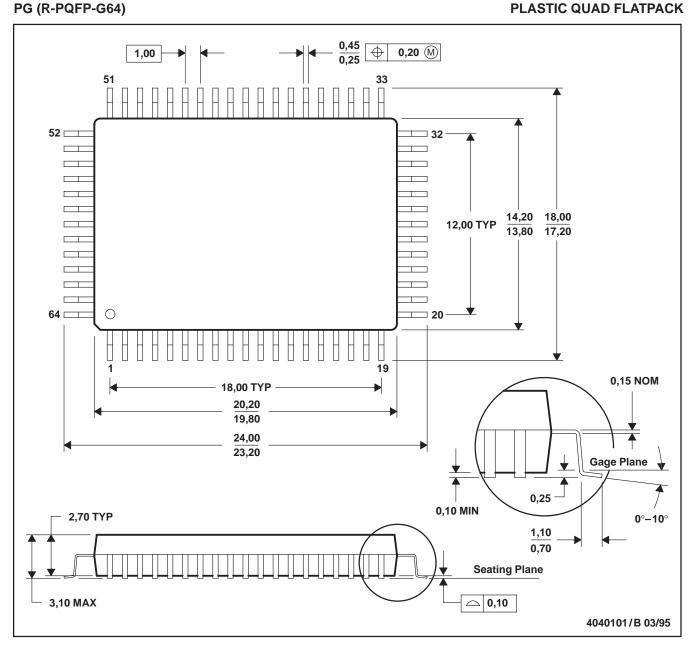

- 64-Pin QFP PG (2402A)

- Extended Temperature Options (A and S)

- A: 40°C to 85°C

- S: 40°C to 125°C

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Code Composer Studio and XDS510 are trademarks of Texas Instruments.

Other trademarks are the property of their respective owners.

<sup>†</sup> IEEE Standard 1149.1–1990, IEEE Standard Test-Access Port; however, boundary scan is not supported in this device family.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

# TMS320LF2407A, TMS320LF2406A, TMS320LF2403A, TMS320LF2402A TMS320LC2406A, TMS320LC2404A, TMS320LC2403A, TMS320LC2402A DSP CONTROLLERS SPRS145L - JULY 2000 - REVISED SEPTEMBER 2007

#### **Table of Contents**

| Description                                   | . 4 |

|-----------------------------------------------|-----|

| TMS320x240xA Device Summary                   | . 5 |

| Functional Block Diagram of the 2407A         |     |

| DSP Controller                                |     |

| Pinouts                                       | . 7 |

| Pin Functions                                 | 11  |

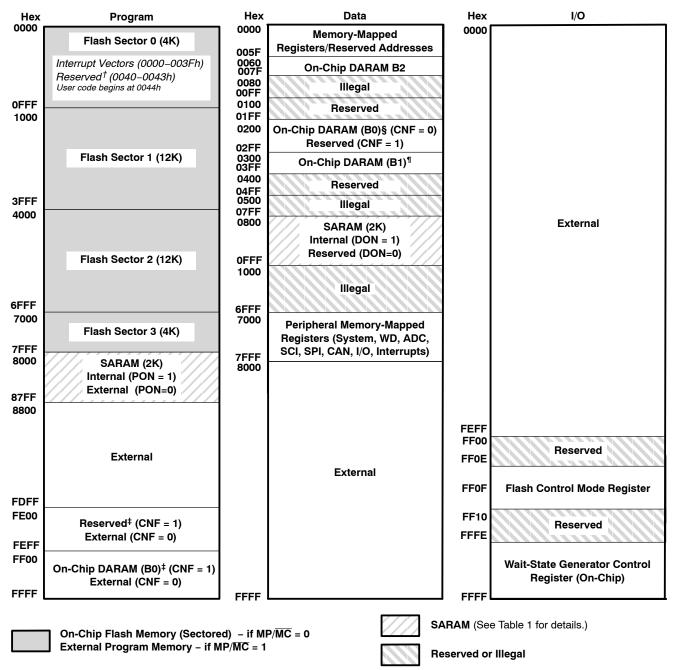

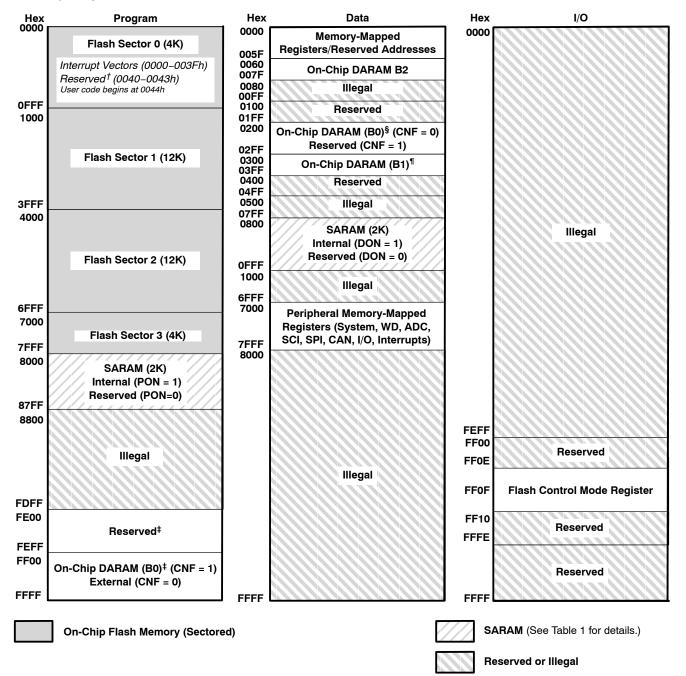

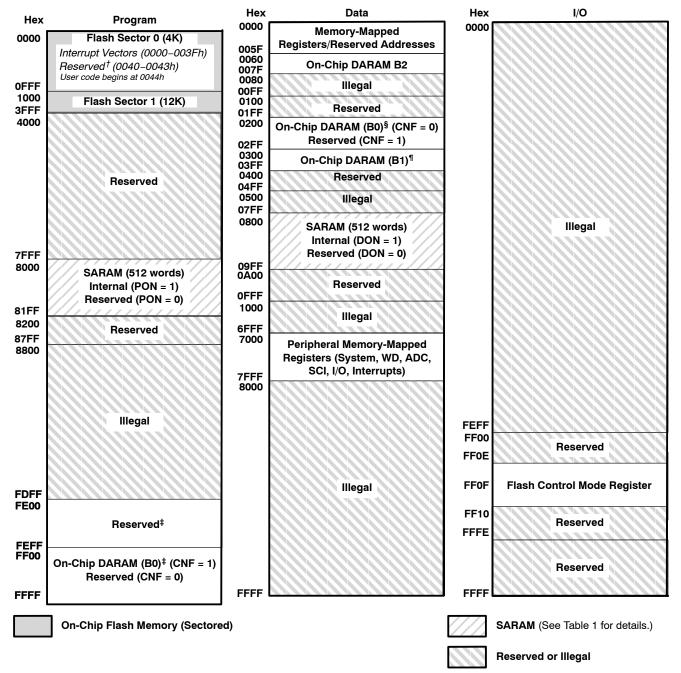

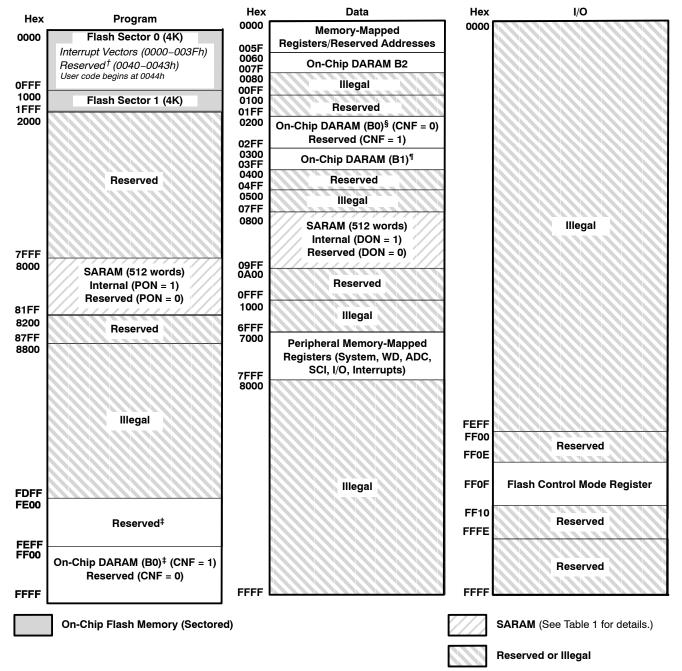

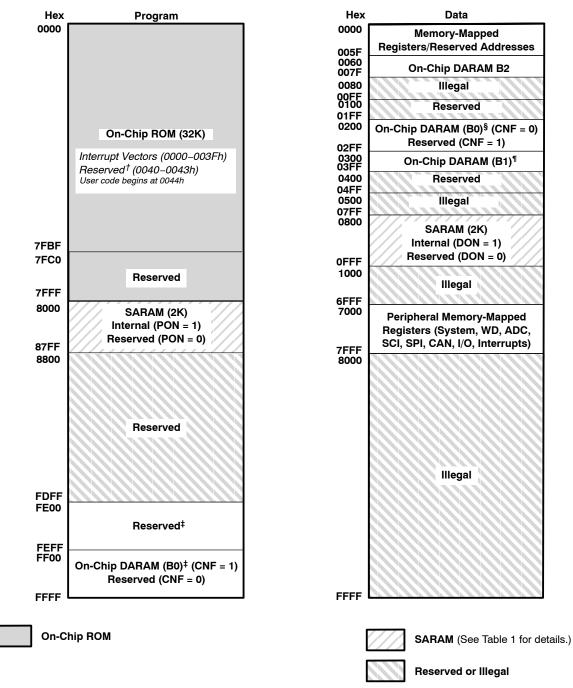

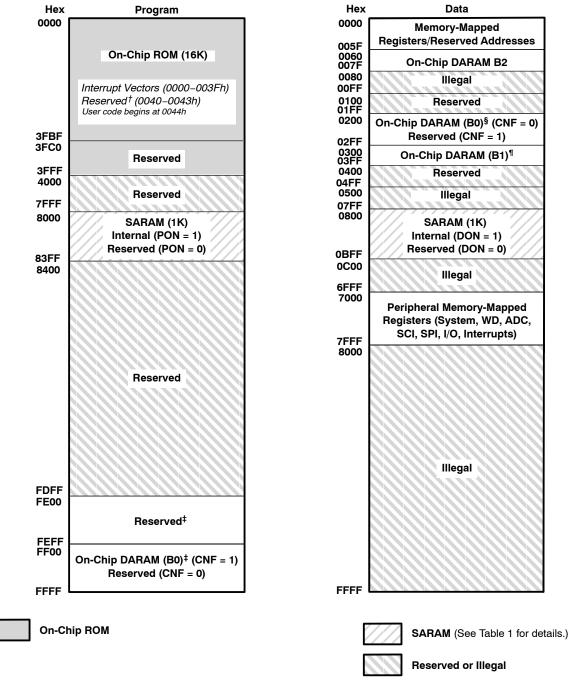

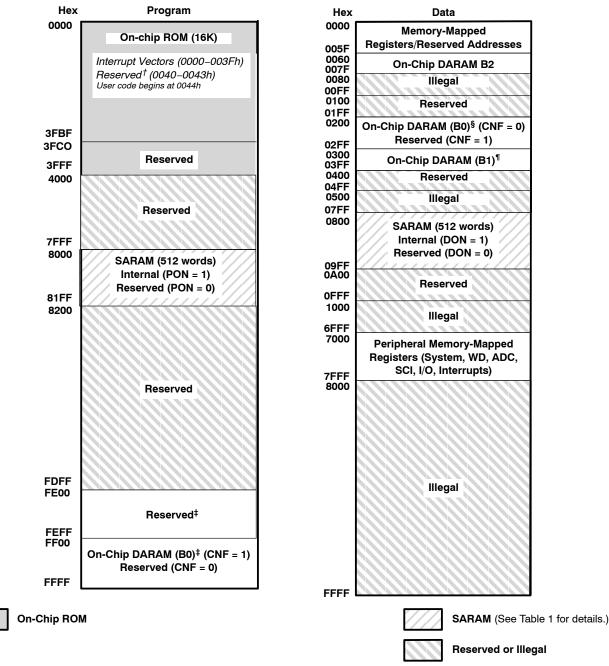

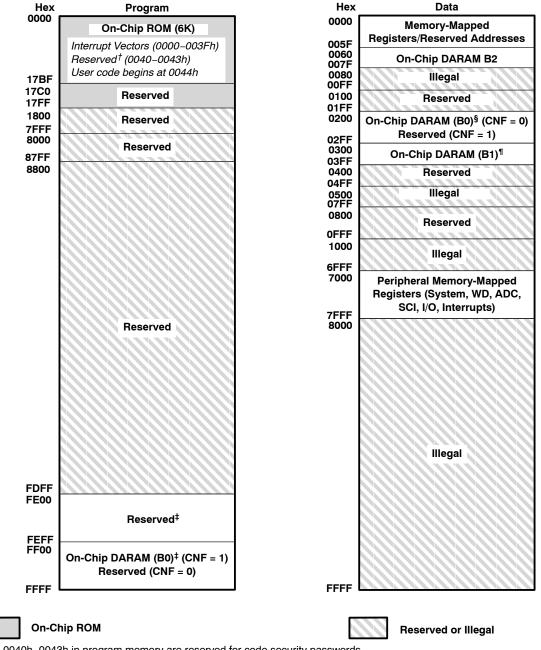

| Memory Maps                                   | 21  |

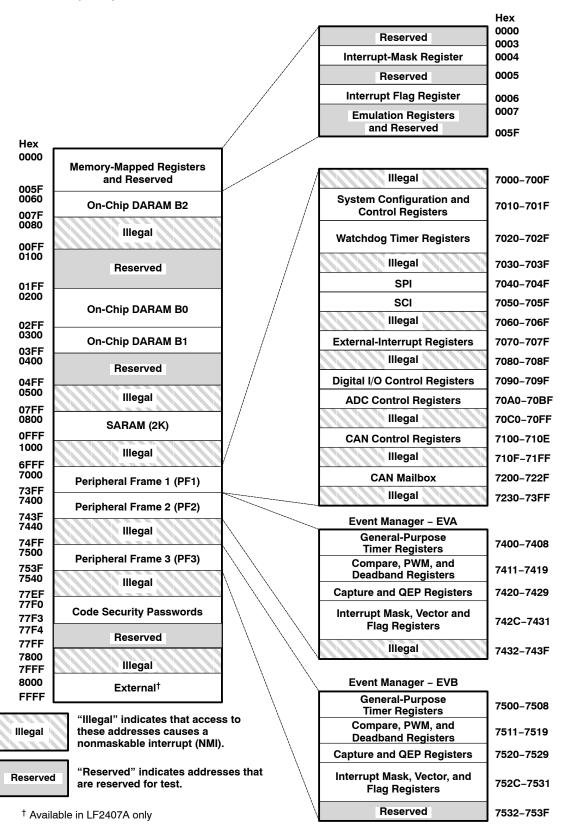

| Peripheral Memory Map of the 2407A/2406A      | 29  |

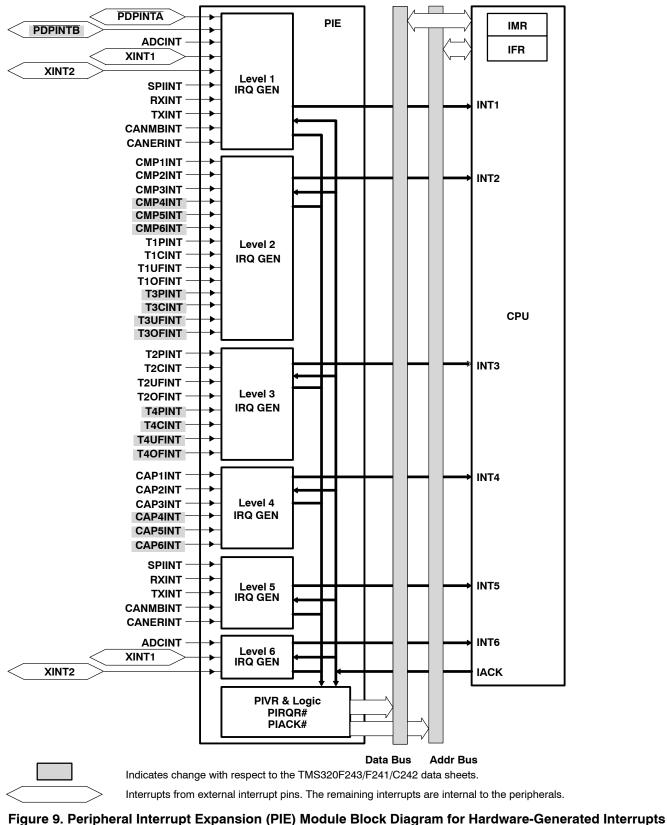

| Device Reset and Interrupts                   | 30  |

| DSP CPU Core                                  | 34  |

| TMS320x240xA Instruction Set                  | 34  |

| Scan-Based Emulation                          | 34  |

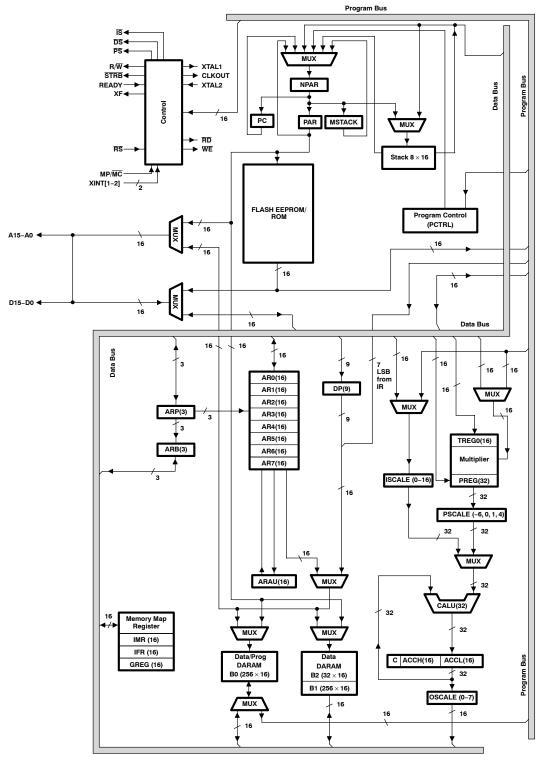

| Functional Block Diagram of the 2407A DSP CPU | 35  |

| Internal Memory                               | 42  |

| Peripherals                                   | 45  |

| Event Manager Modules (EVA, EVB)              | 45  |

| Enhanced Analog-to-Digital Converter          |     |

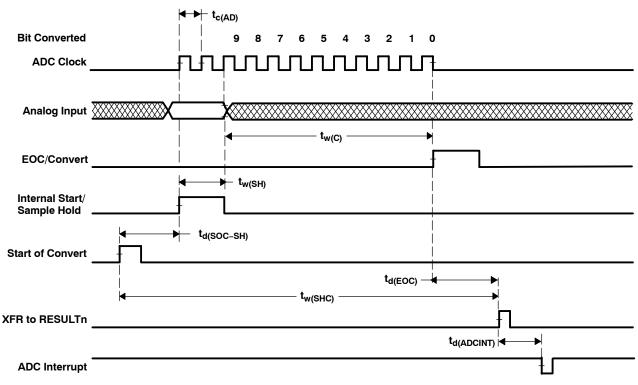

| (ADC) Module                                  | 49  |

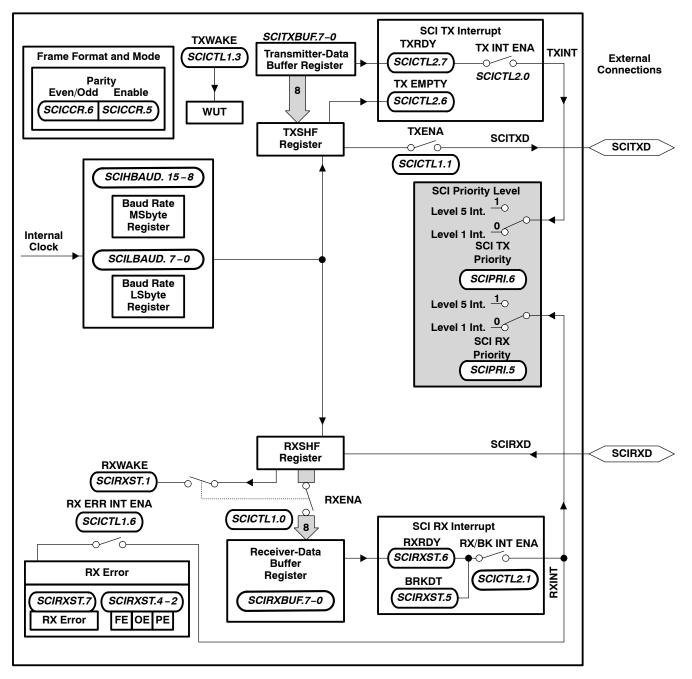

| Serial Communications Interface (SCI) Module  | 53  |

|                                               |     |

| Controller Area Network (CAN) Module51Serial Peripheral Interface (SPI) Module55PLL-Based Clock Module57Digital I/O and Shared Pin Functions60External Memory Interface (LF2407A)64Watchdog (WD) Timer Module65Development Support67Documentation Support70 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LF240xA and LC240xA Electrical                                                                                                                                                                                                                              |

| Specifications Data 71                                                                                                                                                                                                                                      |

| Absolute Maximum Ratings 71                                                                                                                                                                                                                                 |

| Recommended Operating Conditions                                                                                                                                                                                                                            |

| Migrating From LF240xA (Flash) Devices to                                                                                                                                                                                                                   |

| LC240xA (ROM) Devices                                                                                                                                                                                                                                       |

| Migrating From 240x Devices to 240xA Devices 111                                                                                                                                                                                                            |

| Migrating From LF240x Devices to                                                                                                                                                                                                                            |

| LC240xA Devices                                                                                                                                                                                                                                             |

| Peripheral Register Description                                                                                                                                                                                                                             |

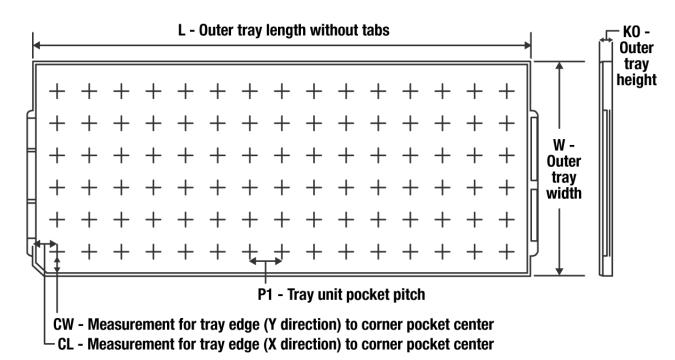

| Mechanical Data 126                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                             |

# TMS320LF2407A, TMS320LF2406A, TMS320LF2403A, TMS320LF2402A TMS320LC2406A, TMS320LC2404A, TMS320LC2403A, TMS320LC2402A DSP CONTROLLERS SPRS145L - JULY 2000 - REVISED SEPTEMBER 2007

## **REVISION HISTORY**

| PAGE | HIGHLIGHTS                                                                                                                                                                |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11   | Added the $V_{CCA}$ pin to final note on Table 2                                                                                                                          |

| 27   | Modified LC2403A memory map (Figure 7) in location 8200                                                                                                                   |

| 50   | Added a sentence to the paragraph following Figure 12                                                                                                                     |

| 59   | Added 1/4 W to second column header in Table 10, Loop Filter Component Values With Damping Factor = 2.0                                                                   |

| 71   | Added a note to recommended operating conditions table                                                                                                                    |

| 72   | Added a note to electrical characteristics table                                                                                                                          |

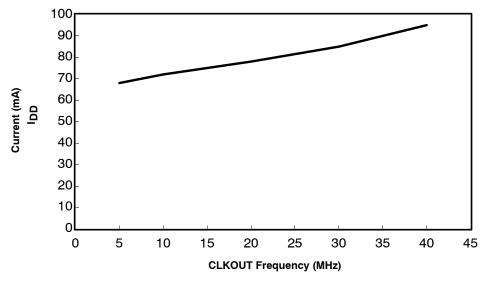

| 77   | Added Figure 23                                                                                                                                                           |

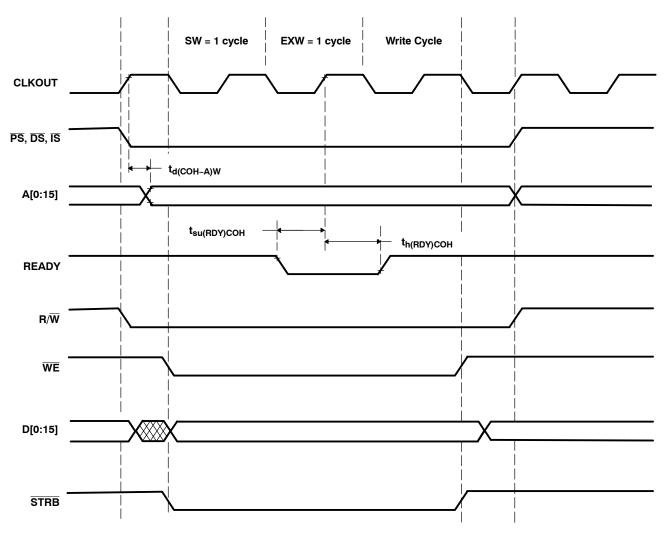

| 101  | Changed parameter td(WRN) in switching characteristics over recommended operating conditions for an external memory interface write at 40 MHz [H = $0.5t_{c(CO)}$ ] table |

| 108  | Changed MAX value for I <sub>CCA</sub> in operating characteristics over recommended operating condition ranges table                                                     |

| 110  | Added note to Table 18                                                                                                                                                    |

SPRS145L - JULY 2000 - REVISED SEPTEMBER 2007

#### description

The TMS320LF240xA and TMS320LC240xA devices, new members of the TMS320C24x<sup>™</sup> generation of digital signal processor (DSP) controllers, are part of the TMS320C2000<sup>™</sup> platform of fixed-point DSPs. The 240xA devices offer the enhanced TMS320<sup>™</sup> DSP architectural design of the C2xx core CPU for low-cost, low-power, and high-performance processing capabilities. Several advanced peripherals, optimized for digital motor and motion control applications, have been integrated to provide a true single-chip DSP controller. While code-compatible with the existing C24x<sup>™</sup> DSP controller devices, the 240xA offers increased processing performance (40 MIPS) and a higher level of peripheral integration. See the *TMS320x240xA Device Summary* section for device-specific features.

The 240xA generation offers an array of memory sizes and different peripherals tailored to meet the specific price/performance points required by various applications. Flash devices of up to 32K words offer a cost-effective reprogrammable solution for volume production. The 240xA devices offer a password-based "code security" feature which is useful in preventing unauthorized duplication of proprietary code stored in on-chip Flash/ROM. Note that Flash-based devices contain a 256-word boot ROM to facilitate in-circuit programming. The 240xA family also includes ROM devices that are fully pin-to-pin compatible with their Flash counterparts.

All 240xA devices offer at least one event manager module which has been optimized for digital motor control and power conversion applications. Capabilities of this module include center- and/or edge-aligned PWM generation, programmable deadband to prevent shoot-through faults, and synchronized analog-to-digital conversion. Devices with dual event managers enable multiple motor and/or converter control with a single 240xA DSP controller. Select EV pins have been provided with an "input-qualifier" circuitry, which minimizes inadvertent pin-triggering by glitches.

The high-performance, 10-bit analog-to-digital converter (ADC) has a minimum conversion time of 375 ns and offers up to 16 channels of analog input. The autosequencing capability of the ADC allows a maximum of 16 conversions to take place in a single conversion session without any CPU overhead.

A serial communications interface (SCI) is integrated on all devices to provide asynchronous communication to other devices in the system. For systems requiring additional communication interfaces, the 2407A, 2406A, 2404A, and 2403A offer a 16-bit synchronous serial peripheral interface (SPI). The 2407A, 2406A, and 2403A offer a controller area network (CAN) communications module that meets 2.0B specifications. To maximize device flexibility, functional pins are also configurable as general-purpose inputs/outputs (GPIOs).

To streamline development time, JTAG-compliant scan-based emulation has been integrated into all devices. This provides non-intrusive real-time capabilities required to debug digital control systems. A complete suite of code-generation tools from C compilers to the industry-standard Code Composer Studio<sup>™</sup> debugger supports this family. Numerous third-party developers not only offer device-level development tools, but also system-level design and development support.

TMS320C24x, TMS320C2000, TMS320, and C24x are trademarks of Texas Instruments.

SPRS145L - JULY 2000 - REVISED SEPTEMBER 2007

## TMS320x240xA device summary

Note that throughout this data sheet, 240xA is used as a generic name for the LF240xA/LC240xA generation of devices.

| FEATUR                                                                                                 | E                             | LF2407A       | LF2406A       | LF2403A      | LF2402A       | LC2406A       | LC2404A       | LC2403A           | LC2402A |

|--------------------------------------------------------------------------------------------------------|-------------------------------|---------------|---------------|--------------|---------------|---------------|---------------|-------------------|---------|

| C2xx DSP Core                                                                                          | Yes                           | Yes           | Yes           | Yes          | Yes           | Yes           | Yes           | Yes               |         |

| Instruction Cycle                                                                                      | 25 ns                         | 25 ns         | 25 ns         | 25 ns        | 25 ns         | 25 ns         | 25 ns         | 25 ns             |         |

| MIPS (40 MHz)                                                                                          | 40 MIPS                       | 40 MIPS       | 40 MIPS       | 40 MIPS      | 40 MIPS       | 40 MIPS       | 40 MIPS       | 40 MIPS           |         |

|                                                                                                        | Dual-Access<br>RAM (DARAM)    | 544           | 544           | 544          | 544           | 544           | 544           | 544               | 544     |

| RAM (16-bit word)                                                                                      | Single-Access<br>RAM (SARAM)  | 2K            | 2K            | 512          | 512           | 2K            | 1K            | 512               | _       |

| 3.3-V On-chip Flash (16-<br>(4 sectors: 4K, 12K, 12K,                                                  |                               | 32K           | 32K           | 16K          | 8K            | _             | _             | _                 | _       |

| On-chip ROM (16-bit wor                                                                                | d)                            |               |               |              |               | 32K           | 16K           | 16K               | 6K      |

| Code Security for On-Chi                                                                               | p Flash/ROM                   | Yes           | Yes           | Yes          | Yes           | Yes           | Yes           | Yes               | Yes     |

| Boot ROM                                                                                               |                               | Yes           | Yes           | Yes          | Yes           | —             | _             | —                 | _       |

| External Memory Interfac                                                                               | e                             | Yes           |               |              |               |               | _             |                   |         |

| Event Managers A and B                                                                                 | (EVA and EVB)                 | EVA,<br>EVB   | EVA,<br>EVB   | EVA          | EVA           | EVA,<br>EVB   | EVA,<br>EVB   | EVA               | EVA     |

| General-Purpo                                                                                          | se (GP) Timers                | 4             | 4             | 2            | 2             | 4             | 4             | 2                 | 2       |

| Compare (CMF                                                                                           | P)/PWM                        | 12/16         | 12/16         | 6/8          | 6/8           | 12/16         | 12/16         | 6/8               | 6/8     |

| Capture (CAP)                                                                                          | /QEP                          | 6/4           | 6/4           | 3/2          | 3/2           | 6/4           | 6/4           | 3/2               | 3/2     |

| <ul> <li>Input qualifier circuitry on<br/>PDPINTx, CAPx, QEPx,<br/>XINT1/2, and ADCSOC pins</li> </ul> |                               | Yes           | Yes           | Yes          | Yes           | Yes           | Yes           | Yes               | Yes     |

| Status of PDPI<br>in COMCONx r                                                                         | NTx pin reflected<br>register | Yes           | Yes           | Yes          | Yes           | Yes           | Yes           | Yes               | Yes     |

| Watchdog Timer                                                                                         |                               | Yes           | Yes           | Yes          | Yes           | Yes           | Yes           | Yes               | Yes     |

| 10-Bit ADC                                                                                             |                               | Yes           | Yes           | Yes          | Yes           | Yes           | Yes           | Yes               | Yes     |

| Channels                                                                                               |                               | 16            | 16            | 8            | 8             | 16            | 16            | 8                 | 8       |

| Conversion Tin                                                                                         | ne (minimum)                  | 500 ns        | 500 ns        | 500 ns       | 500 ns        | 500 ns        | 500 ns        | 500 ns            | 500 ns  |

| SPI                                                                                                    |                               | Yes           | Yes           | Yes          |               | Yes           | Yes           | Yes               |         |

| SCI                                                                                                    |                               | Yes           | Yes           | Yes          | Yes           | Yes           | Yes           | Yes               | Yes     |

| CAN                                                                                                    |                               | Yes           | Yes           | Yes          | _             | Yes           | _             | Yes               | —       |

| Digital I/O Pins<br>(Shared)                                                                           |                               | 41            | 41            | 21           | 21            | 41            | 41            | 21                | 21      |

| External Interrupts                                                                                    | 5                             | 5             | 3             | 3            | 5             | 5             | 3             | 3                 |         |

| Supply Voltage                                                                                         | 3.3 V                         | 3.3 V         | 3.3 V         | 3.3 V        | 3.3 V         | 3.3 V         | 3.3 V         | 3.3 V             |         |

| Packaging                                                                                              | 144-pin<br>PGE                | 100-pin<br>PZ | 64-pin<br>PAG | 64-pin<br>PG | 100-pin<br>PZ | 100-pin<br>PZ | 64-pin<br>PAG | 64-pin<br>PG, PAG |         |

| Product Status:<br>Product Preview (PP)<br>Advance Information<br>Production Data (PD)                 | (AI)                          | PD            | PD            | PD           | PD            | PD            | PD            | PD                | PD      |

#### Table 1. Hardware Features of 240xA Devices

Denotes features that are different/new compared to 240x devices.

SPRS145L - JULY 2000 - REVISED SEPTEMBER 2007

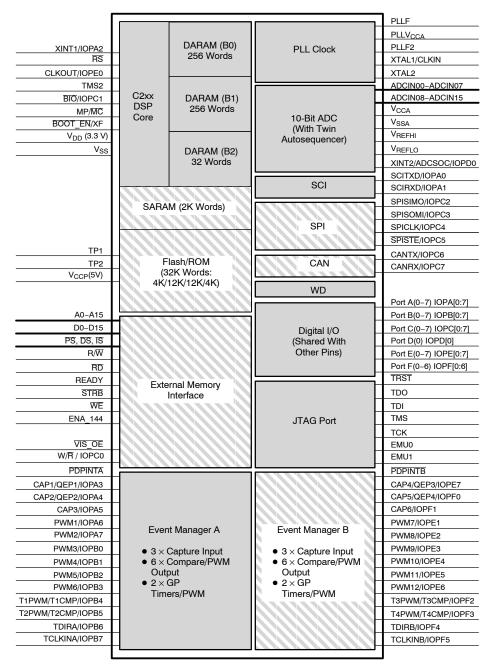

#### functional block diagram of the 2407A DSP controller

Indicates optional modules.

The memory size and peripheral selection of these modules change for different 240xA devices. See Table 1 for device-specific details.

SPRS145L - JULY 2000 - REVISED SEPTEMBER 2007

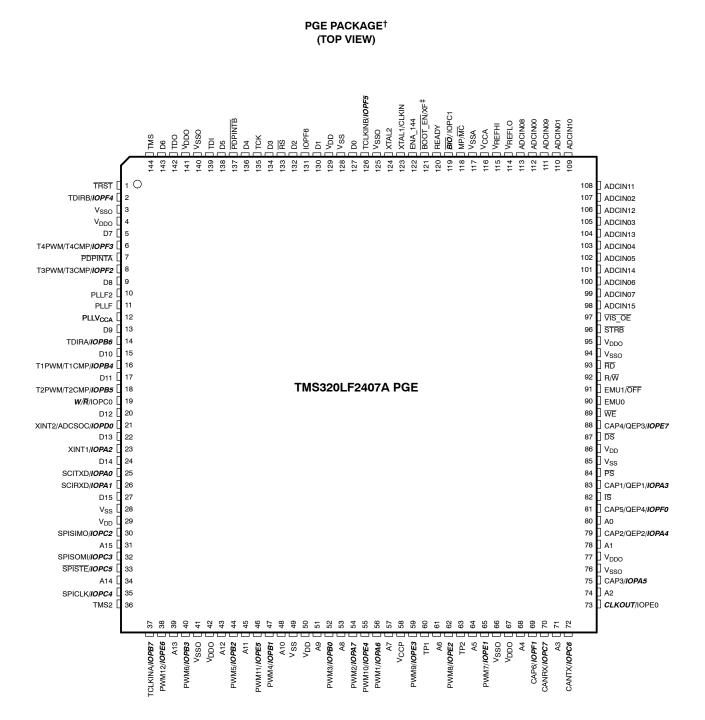

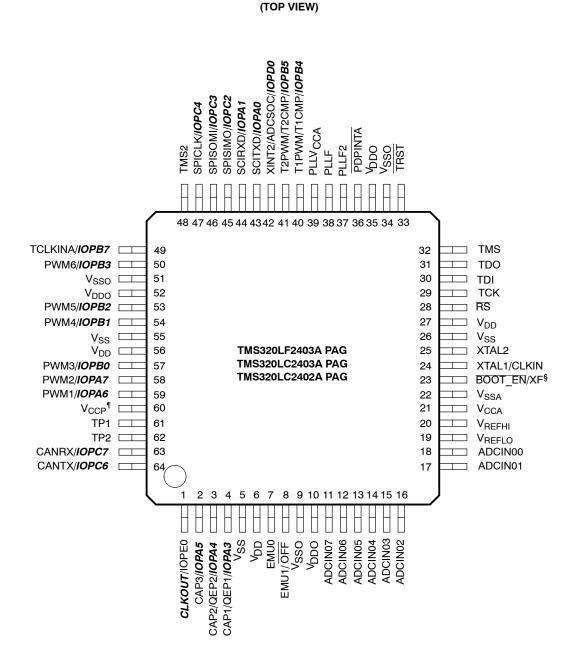

#### pinouts

<sup>†</sup> Bold, italicized pin names indicate pin function after reset.

<sup>‡</sup> BOOT\_EN is available only on Flash devices.

SPRS145L - JULY 2000 - REVISED SEPTEMBER 2007

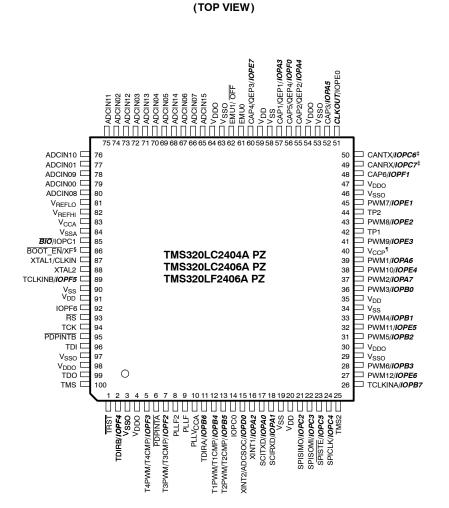

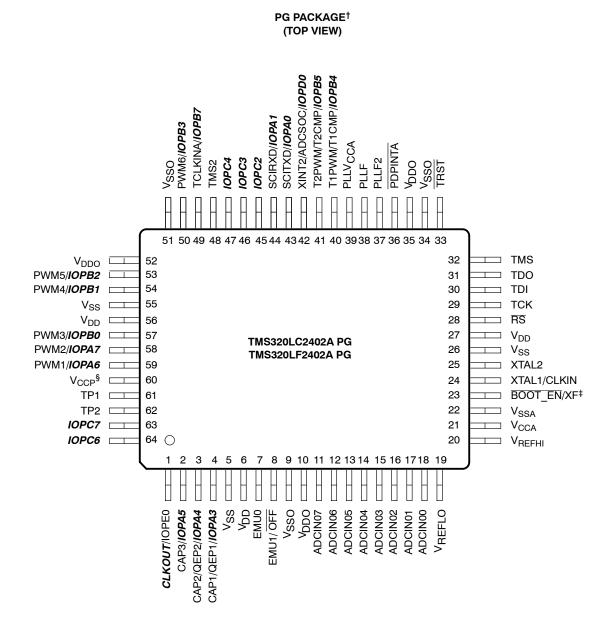

#### pinouts (continued)

PZ PACKAGE<sup>†</sup>

<sup>†</sup> Bold, italicized pin names indicate pin function after reset.

<sup>‡</sup> CANTX and CANRX are not available on LC2404A devices.

§ BOOT\_EN is available only on Flash devices.

<sup>¶</sup> On the ROM devices (LC240xA), V<sub>CCP</sub> is a No Connect (NC).

SPRS145L - JULY 2000 - REVISED SEPTEMBER 2007

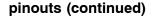

PAG PACKAGE<sup>†‡</sup>

<sup>†</sup> Bold, italicized pin names indicate pin function after reset.

<sup>‡</sup> For LC2402A, the following pins are different from what is shown:

| Pin 45: | IOPC2 |

|---------|-------|

|         |       |

| Pin 46: | IOPC3 |

| Pin 47  | IOPC4 |

- Pin 63: IOPC7

- Pin 64: IOPC6

§ BOOT\_EN is available only on flash devices.

$^{\P}$  On the ROM devices (LC240xA), V<sub>CCP</sub> is a No Connect (NC).

SPRS145L - JULY 2000 - REVISED SEPTEMBER 2007

#### pinouts (continued)

<sup>†</sup> Bold, italicized pin names indicate pin function after reset.

<sup>‡</sup> BOOT\_EN is available only on Flash devices.

§ On the ROM devices (LC240xA), V<sub>CCP</sub> is a No Connect (NC).

DSP CONTROLLERS SPRS145L – JULY 2000 – REVISED SEPTEMBER 2007

## pin functions

The TMS320LF2407A device is the superset of all the 240xA devices. All signals are available on the 2407A device. Table 2 lists the signals available in the 240xA generation of devices.

| PIN NAME                | LF2407A<br>(144-PGE) | 2406A<br>(100-PZ) | LC2404A<br>(100-PZ) | 2403A,<br>LC2402A<br>(64-PAG)<br>and<br>2402A<br>(64-PG) | DESCRIPTION                                                                                                                                                        |  |  |  |  |  |  |

|-------------------------|----------------------|-------------------|---------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| EVENT MANAGER A (EVA)   |                      |                   |                     |                                                          |                                                                                                                                                                    |  |  |  |  |  |  |

| CAP1/QEP1/ <i>IOPA3</i> | 83                   | 57                | 57                  | 4                                                        | Capture input #1/quadrature encoder pulse input #1 (EVA) or GPIO $(\uparrow)$                                                                                      |  |  |  |  |  |  |

| CAP2/QEP2/ <b>IOPA4</b> | 79                   | 55                | 55                  | 3                                                        | Capture input #2/quadrature encoder pulse input #2 (EVA) or GPIO (1)                                                                                               |  |  |  |  |  |  |

| CAP3/ <i>IOPA5</i>      | 75                   | 52                | 52                  | 2                                                        | Capture input #3 (EVA) or GPIO (1)                                                                                                                                 |  |  |  |  |  |  |

| PWM1/ <i>IOPA6</i>      | 56                   | 39                | 39                  | 59                                                       | Compare/PWM output pin #1 (EVA) or GPIO (1)                                                                                                                        |  |  |  |  |  |  |

| PWM2/ <b>IOPA7</b>      | 54                   | 37                | 37                  | 58                                                       | Compare/PWM output pin #2 (EVA) or GPIO (1)                                                                                                                        |  |  |  |  |  |  |

| PWM3/ <i>IOPB0</i>      | 52                   | 36                | 36                  | 57                                                       | Compare/PWM output pin #3 (EVA) or GPIO (1)                                                                                                                        |  |  |  |  |  |  |

| PWM4/ <i>IOPB1</i>      | 47                   | 33                | 33                  | 54                                                       | Compare/PWM output pin #4 (EVA) or GPIO (1)                                                                                                                        |  |  |  |  |  |  |

| PWM5/ <i>IOPB2</i>      | 44                   | 31                | 31                  | 53                                                       | Compare/PWM output pin #5 (EVA) or GPIO (1)                                                                                                                        |  |  |  |  |  |  |

| PWM6/ <i>IOPB3</i>      | 40                   | 28                | 28                  | 50                                                       | Compare/PWM output pin #6 (EVA) or GPIO (1)                                                                                                                        |  |  |  |  |  |  |

| T1PWM/T1CMP/IOPB4       | 16                   | 12                | 12                  | 40                                                       | Timer 1 compare output (EVA) or GPIO (1)                                                                                                                           |  |  |  |  |  |  |

| T2PWM/T2CMP/IOPB5       | 18                   | 13                | 13                  | 41                                                       | Timer 2 compare output (EVA) or GPIO (1)                                                                                                                           |  |  |  |  |  |  |

| TDIRA/ <b>IOPB6</b>     | 14                   | 11                | 11                  |                                                          | Counting direction for general-purpose (GP) timer (EVA) or<br>GPIO. If TDIRA = 1, upward counting is selected. If<br>TDIRA = 0, downward counting is selected. (1) |  |  |  |  |  |  |

| TCLKINA/ <i>IOPB7</i>   | 37                   | 26                | 26                  | 49                                                       | External clock input for GP timer (EVA) or GPIO. Note that the timer can also use the internal device clock. $(\uparrow)$                                          |  |  |  |  |  |  |

|                         | •                    | •                 | EVENT               | MANAGER E                                                | B (EVB)                                                                                                                                                            |  |  |  |  |  |  |

| CAP4/QEP3/ <i>IOPE7</i> | 88                   | 60                | 60                  |                                                          | Capture input #4/quadrature encoder pulse input #3 (EVB) or GPIO $(\uparrow)$                                                                                      |  |  |  |  |  |  |

| CAP5/QEP4/ <b>IOPF0</b> | 81                   | 56                | 56                  |                                                          | Capture input #5/quadrature encoder pulse input #4 (EVB) or GPIO (1)                                                                                               |  |  |  |  |  |  |

| CAP6/ <b>IOPF1</b>      | 69                   | 48                | 48                  |                                                          | Capture input #6 (EVB) or GPIO (1)                                                                                                                                 |  |  |  |  |  |  |

| PWM7/ <b>IOPE1</b>      | 65                   | 45                | 45                  |                                                          | Compare/PWM output pin #7 (EVB) or GPIO (1)                                                                                                                        |  |  |  |  |  |  |

| PWM8/ <i>IOPE2</i>      | 62                   | 43                | 43                  |                                                          | Compare/PWM output pin #8 (EVB) or GPIO (1)                                                                                                                        |  |  |  |  |  |  |

| PWM9/ <i>IOPE3</i>      | 59                   | 41                | 41                  |                                                          | Compare/PWM output pin #9 (EVB) or GPIO (1)                                                                                                                        |  |  |  |  |  |  |

| PWM10/ <i>IOPE4</i>     | 55                   | 38                | 38                  |                                                          | Compare/PWM output pin #10 (EVB) or GPIO (1)                                                                                                                       |  |  |  |  |  |  |

| PWM11/ <i>IOPE5</i>     | 46                   | 32                | 32                  |                                                          | Compare/PWM output pin #11 (EVB) or GPIO (1)                                                                                                                       |  |  |  |  |  |  |

| PWM12/ <i>IOPE6</i>     | 38                   | 27                | 27                  |                                                          | Compare/PWM output pin #12 (EVB) or GPIO (1)                                                                                                                       |  |  |  |  |  |  |

| Table 2. LF240xA and LC240xA Pin List and Package Option | ıs†‡ |

|----------------------------------------------------------|------|

|----------------------------------------------------------|------|

<sup>†</sup> Bold, italicized pin names indicate pin function after reset.

<sup>‡</sup> GPIO – General-purpose input/output pin. All GPIOs come up as input after reset.

§ It is highly recommended that V<sub>CCA</sub> be isolated from the digital supply voltage (and V<sub>SSA</sub> from digital ground) to maintain the specified accuracy and improve the noise immunity of the ADC.

<sup>¶</sup> Only when all of the following conditions are met: EMU1/OFF is low, TRST is low, and EMU0 is high

<sup>#</sup> No power supply pin (V<sub>DD</sub>, V<sub>DDO</sub>, V<sub>CCA</sub>, V<sub>SS</sub>, or V<sub>SSO</sub>) should be left unconnected. All power supply pins must be connected appropriately for proper device operation.

SPRS145L - JULY 2000 - REVISED SEPTEMBER 2007

## pin functions (continued)

## Table 2. LF240xA and LC240xA Pin List and Package Options<sup>†‡</sup> (Continued)

| PIN NAME                          | LF2407A<br>(144-PGE) | 2406A<br>(100-PZ) | LC2404A<br>(100-PZ) | 2403A,<br>LC2402A<br>(64-PAG)<br>and<br>2402A<br>(64-PG) | DESCRIPTION                                                                                                                                                             |  |  |  |  |  |  |

|-----------------------------------|----------------------|-------------------|---------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| EVENT MANAGER B (EVB) (CONTINUED) |                      |                   |                     |                                                          |                                                                                                                                                                         |  |  |  |  |  |  |

| T3PWM/T3CMP/ <i>IOPF2</i>         | 8                    | 7                 | 7                   |                                                          | Timer 3 compare output (EVB) or GPIO (1)                                                                                                                                |  |  |  |  |  |  |

| T4PWM/T4CMP/ <i>IOPF3</i>         | 6                    | 5                 | 5                   |                                                          | Timer 4 compare output (EVB) or GPIO $(\uparrow)$                                                                                                                       |  |  |  |  |  |  |

| TDIRB/ <b>IOPF4</b>               | 2                    | 2                 | 2                   |                                                          | Counting direction for general-purpose (GP) timer (EVB) or GPIO. If TDIRB = 1, upward counting is selected. If TDIRB = 0, downward counting is selected. ( $\uparrow$ ) |  |  |  |  |  |  |

| TCLKINB/ <i>IOPF5</i>             | 126                  | 89                | 89                  |                                                          | External clock input for GP timer (EVB) or GPIO. Note that the timer can also use the internal device clock. $(\uparrow)$                                               |  |  |  |  |  |  |

|                                   | ANA                  | LOG-TO-D          | IGITAL CO           | NVERTER (A                                               | DC)                                                                                                                                                                     |  |  |  |  |  |  |

| ADCIN00                           | 112                  | 79                | 79                  | 18                                                       | Analog input #0 to the ADC                                                                                                                                              |  |  |  |  |  |  |

| ADCIN01                           | 110                  | 77                | 77                  | 17                                                       | Analog input #1 to the ADC                                                                                                                                              |  |  |  |  |  |  |

| ADCIN02                           | 107                  | 74                | 74                  | 16                                                       | Analog input #2 to the ADC                                                                                                                                              |  |  |  |  |  |  |

| ADCIN03                           | 105                  | 72                | 72                  | 15                                                       | Analog input #3 to the ADC                                                                                                                                              |  |  |  |  |  |  |

| ADCIN04                           | 103                  | 70                | 70                  | 14                                                       | Analog input #4 to the ADC                                                                                                                                              |  |  |  |  |  |  |

| ADCIN05                           | 102                  | 69                | 69                  | 13                                                       | Analog input #5 to the ADC                                                                                                                                              |  |  |  |  |  |  |

| ADCIN06                           | 100                  | 67                | 67                  | 12                                                       | Analog input #6 to the ADC                                                                                                                                              |  |  |  |  |  |  |

| ADCIN07                           | 99                   | 66                | 66                  | 11                                                       | Analog input #7 to the ADC                                                                                                                                              |  |  |  |  |  |  |

| ADCIN08                           | 113                  | 80                | 80                  |                                                          | Analog input #8 to the ADC                                                                                                                                              |  |  |  |  |  |  |

| ADCIN09                           | 111                  | 78                | 78                  |                                                          | Analog input #9 to the ADC                                                                                                                                              |  |  |  |  |  |  |

| ADCIN10                           | 109                  | 76                | 76                  |                                                          | Analog input #10 to the ADC                                                                                                                                             |  |  |  |  |  |  |

| ADCIN11                           | 108                  | 75                | 75                  |                                                          | Analog input #11 to the ADC                                                                                                                                             |  |  |  |  |  |  |

| ADCIN12                           | 106                  | 73                | 73                  |                                                          | Analog input #12 to the ADC                                                                                                                                             |  |  |  |  |  |  |

| ADCIN13                           | 104                  | 71                | 71                  |                                                          | Analog input #13 to the ADC                                                                                                                                             |  |  |  |  |  |  |

| ADCIN14                           | 101                  | 68                | 68                  |                                                          | Analog input #14 to the ADC                                                                                                                                             |  |  |  |  |  |  |

| ADCIN15                           | 98                   | 65                | 65                  |                                                          | Analog input #15 to the ADC                                                                                                                                             |  |  |  |  |  |  |

| V <sub>REFHI</sub>                | 115                  | 82                | 82                  | 20                                                       | ADC analog high-voltage reference input                                                                                                                                 |  |  |  |  |  |  |

| V <sub>REFLO</sub>                | 114                  | 81                | 81                  | 19                                                       | ADC analog low-voltage reference input                                                                                                                                  |  |  |  |  |  |  |

| V <sub>CCA</sub>                  | 116                  | 83                | 83                  | 21                                                       | Analog supply voltage for ADC $(3.3 \text{ V})^{\$}$                                                                                                                    |  |  |  |  |  |  |

| V <sub>SSA</sub>                  | 117                  | 84                | 84                  | 22                                                       | Analog ground reference for ADC                                                                                                                                         |  |  |  |  |  |  |

<sup>†</sup> Bold, italicized pin names indicate pin function after reset.

<sup>‡</sup> GPIO – General-purpose input/output pin. All GPIOs come up as input after reset.

§ It is highly recommended that V<sub>CCA</sub> be isolated from the digital supply voltage (and V<sub>SSA</sub> from digital ground) to maintain the specified accuracy and improve the noise immunity of the ADC.

<sup>¶</sup> Only when all of the following conditions are met: EMU1/OFF is low, TRST is low, and EMU0 is high

<sup>#</sup> No power supply pin (V<sub>DD</sub>, V<sub>DDO</sub>, V<sub>CCA</sub>, V<sub>SS</sub>, or V<sub>SSO</sub>) should be left unconnected. All power supply pins must be connected appropriately for proper device operation.

DSP CONTROLLERS SPRS145L – JULY 2000 – REVISED SEPTEMBER 2007

## pin functions (continued)

## Table 2. LF240xA and LC240xA Pin List and Package Options<sup>†‡</sup> (Continued)

| PIN NAME             |           | LF2407A<br>(144-PGE) | 2406A<br>(100-PZ) | LC2404A<br>(100-PZ) | 2403A,<br>LC2402A<br>(64-PAG)<br>and<br>2402A<br>(64-PG) | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------|-----------|----------------------|-------------------|---------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CONTROLLER A         | AREA NETW | /ORK (CAN),          | SERIAL CO         | OMMUNICA            | TIONS INTER                                              | RFACE (SCI), SERIAL PERIPHERAL INTERFACE (SPI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CANRX/ <i>IOPC7</i>  | CANRX     | 70                   | 49                | -                   | 63                                                       | CAN receive data or GPIO (LF2403A) $(\uparrow)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CANHA/IOPC7          | IOPC7     | 70                   | 49                | 49                  | 63                                                       | GPIO only (2402A) (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CANTY/ORCE           | CANTX     | 72                   | 50                | -                   | 64                                                       | CAN transmit data or GPIO (LF2403A) (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CANTX/ <i>IOPC6</i>  | IOPC6     | 72                   | 50                | 50                  | 64                                                       | GPIO only (2402A) (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SCITXD/IOPA0         |           | 25                   | 17                | 17                  | 43                                                       | SCI asynchronous serial port transmit data or GPIO $(\uparrow)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SCIRXD/IOPA1         |           | 26                   | 18                | 18                  | 44                                                       | SCI asynchronous serial port receive data or or GPIO $(\uparrow)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                      | SPICLK    | 35                   | 24                | 24                  | 47                                                       | SPI clock or GPIO (LF2403A) (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SPICLK/ <b>IOPC4</b> | IOPC4     | 35                   | 24                | 24                  | 47                                                       | GPIO only (2402A) (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                      | SPISIMO   | 30                   | 21                | 21                  | 45                                                       | SPI slave in, master out or GPIO (LF2403A) (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SPISIMO/IOPC2        | IOPC2     | 30                   | 21                | 21                  | 45                                                       | GPIO only (2402A) (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                      | SPISOMI   | 32                   | 22                | 22                  | 46                                                       | SPI slave out, master in or GPIO (LF2403A) (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SPISOMI/IOPC3        | IOPC3     | 32                   | 22                | 22                  | 46                                                       | GPIO only (2402A) (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                      | SPISTE    | 33                   | 23                | 23                  | -                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SPISTE/IOPC5         | IOPC5     | 33                   | 23                | 23                  | -                                                        | SPI slave transmit-enable (optional) or GPIO (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                      |           |                      | EXT               | ERNAL INT           | ERRUPTS, C                                               | LOCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

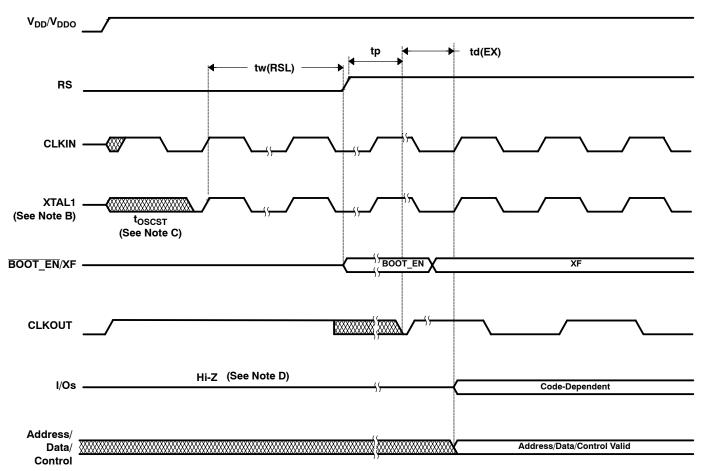

| RS                   |           | 133                  | 93                | 93                  | 28                                                       | Device Reset (in) and Watchdog Reset (out).<br>Device reset. $\overline{RS}$ causes the device to terminate execution<br>and to set PC = 0. When $\overline{RS}$ is brought to a high level,<br>execution begins at location 0x0000 of program memory.<br>This pin is driven low by the DSP when a watchdog reset<br>occurs. During watchdog reset, the $\overline{RS}$ pin will be driven<br>low for the watchdog reset duration of 128 CLKIN cycles.<br>The output buffer of this pin is an open-drain with an<br>internal pullup (20 $\mu$ A, typical). It is recommended that this<br>pin be driven by an open-drain device. (1) |

| PDPINTA              |           | 7                    | 6                 | 6                   | 36                                                       | Power drive protection interrupt input. This interrupt, when activated, puts the PWM output pins (EVA) in the high-impedance state should motor drive/power converter abnormalities, such as overvoltage or overcurrent, etc., arise. PDPINTA is a falling-edge-sensitive interrupt. (1)                                                                                                                                                                                                                                                                                                                                             |

<sup>†</sup> Bold, italicized pin names indicate pin function after reset.

<sup>‡</sup> GPIO – General-purpose input/output pin. All GPIOs come up as input after reset.

It is highly recommended that V<sub>CCA</sub> be isolated from the digital supply voltage (and V<sub>SSA</sub> from digital ground) to maintain the specified accuracy and improve the noise immunity of the ADC.

<sup>¶</sup> Only when all of the following conditions are met: EMU1/OFF is low, TRST is low, and EMU0 is high

<sup>#</sup> No power supply pin (V<sub>DD</sub>, V<sub>DDO</sub>, V<sub>CCA</sub>, V<sub>SS</sub>, or V<sub>SSO</sub>) should be left unconnected. All power supply pins must be connected appropriately for proper device operation.

SPRS145L - JULY 2000 - REVISED SEPTEMBER 2007

#### pin functions (continued)

## Table 2. LF240xA and LC240xA Pin List and Package Options<sup>†‡</sup> (Continued)

| PIN NAME            |                 | LF2407A<br>(144-PGE) | 2406A LC2404A (64-PAG)<br>(100-PZ) (100-PZ) and<br>2402A<br>(64-PG) |            | LC2402A<br>(64-PAG)<br>and<br>2402A<br>(64-PG) | DESCRIPTION                                                                                                                                                                                                                                                                                                        |  |  |

|---------------------|-----------------|----------------------|---------------------------------------------------------------------|------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                     |                 |                      | EXTERNAL                                                            | . INTERRUP | PTS, CLOCK                                     | (CONTINUED)                                                                                                                                                                                                                                                                                                        |  |  |

| XINT1/ <b>IOPA2</b> |                 | 23                   | 16                                                                  | 16         |                                                | External user interrupt 1 or GPIO. Both XINT1 and XINT2 are edge-sensitive. The edge polarity is programmable. (1)                                                                                                                                                                                                 |  |  |

| XINT2/ADCSO         | C/ <b>IOPD0</b> | 21                   | 15                                                                  | 15         | 42                                             | External user interrupt 2 and ADC start of conversion or GPIO. External "start-of-conversion" input for ADC/GPIO. Both XINT1 and XINT2 are edge-sensitive. The edge polarity is programmable. (1)                                                                                                                  |  |  |

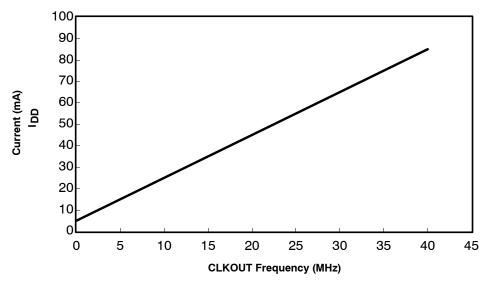

| <i>CLKOUT</i> /IOPE | 0               | 73                   | 51                                                                  | 51         | 1                                              | Clock output or GPIO. This pin outputs either the CPU clock (CLKOUT) or the watchdog clock (WDCLK). The selection is made by the CLKSRC bit (bit 14) of the system control and status register (SCSR). This pin can be used as a GPIO if not used as a clock output pin. $(\uparrow)$                              |  |  |

| PDPINTB             |                 | 137                  | 95                                                                  | 95         |                                                | Power drive protection interrupt input. This interrupt, when activated, puts the PWM output pins (EVB) in the high-impedance state should motor drive/power converter abnormalities, such as overvoltage or overcurrent, etc., arise. $\overrightarrow{\text{PDPINTB}}$ is a falling-edge-sensitive interrupt. (1) |  |  |

|                     |                 | OSC                  | ILLATOR, P                                                          | LL, FLASH  | , BOOT, AND                                    | MISCELLANEOUS                                                                                                                                                                                                                                                                                                      |  |  |

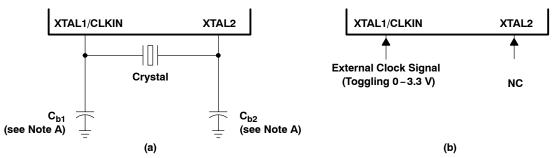

| XTAL1/CLKIN         |                 | 123                  | 87                                                                  | 87         | 24                                             | PLL oscillator input pin. Crystal input to PLL/clock source input to PLL. XTAL1/CLKIN is tied to one side of a reference crystal.                                                                                                                                                                                  |  |  |

| XTAL2               |                 | 124                  | 88                                                                  | 88         | 25                                             | Crystal output. PLL oscillator output pin. XTAL2 is tied to<br>one side of a reference crystal. This pin goes in the<br>high-impedance state when EMU1/OFF is active low.                                                                                                                                          |  |  |

| PLLV <sub>CCA</sub> |                 | 12                   | 10                                                                  | 10         | 39                                             | PLL supply (3.3 V)                                                                                                                                                                                                                                                                                                 |  |  |

| IOPF6               |                 | 131                  | 92                                                                  | 92         |                                                | General-purpose I/O (1)                                                                                                                                                                                                                                                                                            |  |  |

| BOOT_EN /           | BOOT_EN         | 121                  | 86                                                                  | _          | 23                                             | Boot ROM enable, GPO, XF. This pin will be sampled as<br>input (BOOT_EN) to update SCSR2.3 (BOOT_EN bit)<br>during reset and then driven as an output signal for XF. After                                                                                                                                         |  |  |

| XF                  | XF              | 121                  | 86                                                                  | 86         | 23                                             | reset, XF is driven high. ROM devices do not have boot<br>ROM, hence, no BOOT_EN modes. The BOOT_EN pin<br>must be driven with a passive circuit only. (1)                                                                                                                                                         |  |  |

| PLLF                |                 | 11                   | 9                                                                   | 9          | 38                                             | PLL loop filter input 1                                                                                                                                                                                                                                                                                            |  |  |

<sup>†</sup> Bold, italicized pin names indicate pin function after reset.

<sup>‡</sup> GPIO – General-purpose input/output pin. All GPIOs come up as input after reset.

§ It is highly recommended that V<sub>CCA</sub> be isolated from the digital supply voltage (and V<sub>SSA</sub> from digital ground) to maintain the specified accuracy and improve the noise immunity of the ADC.

<sup>¶</sup> Only when all of the following conditions are met: EMU1/OFF is low, TRST is low, and EMU0 is high

<sup>#</sup> No power supply pin (V<sub>DD</sub>, V<sub>DDO</sub>, V<sub>CCA</sub>, V<sub>SS</sub>, or V<sub>SSO</sub>) should be left unconnected. All power supply pins must be connected appropriately for proper device operation.

DSP CONTROLLERS SPRS145L – JULY 2000 – REVISED SEPTEMBER 2007

## pin functions (continued)

| PIN NAME                                                    | LF2407A<br>(144-PGE) | 2406A<br>(100-PZ) | LC2404A<br>(100-PZ) | 2403A,<br>LC2402A<br>(64-PAG)<br>and<br>2402A<br>(64-PG) | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|-------------------------------------------------------------|----------------------|-------------------|---------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| OSCILLATOR, PLL, FLASH, BOOT, AND MISCELLANEOUS (CONTINUED) |                      |                   |                     |                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| PLLF2                                                       | 10                   | 8                 | 8                   | 37                                                       | PLL loop filter input 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| V <sub>CCP</sub> (5V)<br>TP1<br>TP2                         | 58<br>60             | 40<br>42<br>44    | 40<br>42<br>44      | 60<br>61<br>62                                           | Flash programming voltage pin. This pin must be connected to<br>a 5-V supply for Flash programming. The Flash cannot be<br>programmed if this pin is connected to GND. When not<br>programming the Flash (i.e., during normal device operation),<br>this pin can either be left connected to the 5-V supply or it can<br>be tied to GND. This pin must not be left floating at any time. Do<br>not use any current-limiting resistor in series with the 5-V supply<br>on this pin. This pin is a "no connect" (NC) on ROM parts (i.e.,<br>this pin is not connected to any circuitry internal to the device).<br>Connecting this pin to 5 V or leaving it open makes no difference<br>on ROM parts.<br>Test pin 1. <i>Do not connect</i> . |  |  |  |  |  |

| 1P2                                                         | 63                   | 44                | 44                  | 62                                                       | Test pin 2. Do not connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| <b>BIO</b> /IOPC1                                           | 119                  | 85                | 85                  |                                                          | Branch control input. $\overrightarrow{BIO}$ is polled by the BCND pma, BIO instruction. If $\overrightarrow{BIO}$ is low, a branch is executed. If $\overrightarrow{BIO}$ is not used, it should be pulled high. This pin is configured as a branch control input by all device resets. It can be used as a GPIO, if not used as a branch control input. (1)                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

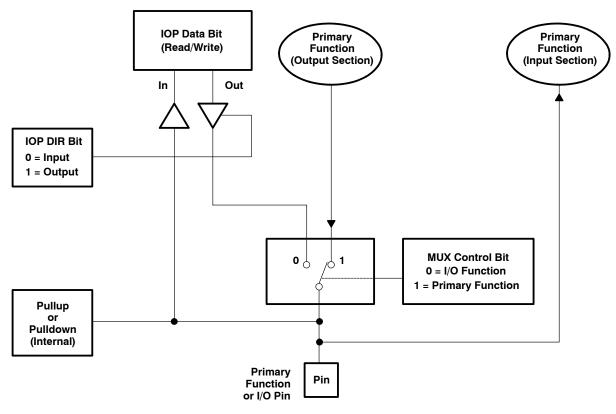

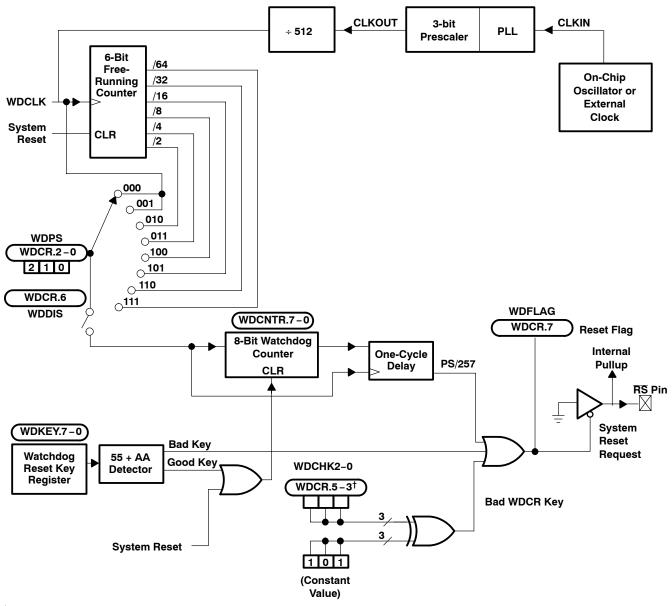

|                                                             |                      |                   | EMUL                | ATION AND                                                | TEST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |